原理图输入法

时间:10-02

整理:3721RD

点击:

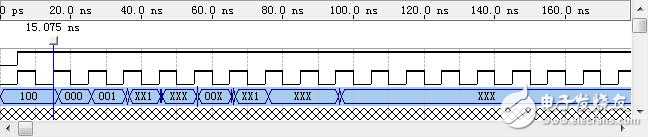

设计一个cpu。 每个模块编译仿真都是正确的,但采用原理图输入法连在一起后,再检测仿真时对模块的输出检测总是错误,例如节拍器状态转换,本来顺序是100,000,111但现在变成100,XX1,XXX 请问这是为什么?非常感谢

示例

出现xx的原因是这几位状态不确定,你在放大视图,看看两个数据之间是不是含有有效的数据在其中。

谢谢。我再仔细瞅瞅,我自己又重新连接了一遍,这次仿真没有出现XX,但原来的原理图仿真之后还是出现,两图对比!看起来没啥区别

老师您好,我又来请教问题了!

我用VHDL设计cpu,然后现在调用LMP_RAM模块,里面放初始数据,单独仿真时输出写入都正常,但连入整体图时,再检测输出却总是为零,也就是没输出

如果可能您留个邮箱,我把我把现在做的发给你,您帮忙看一下

呵呵,互相学习了。我的邮箱是 youzizhile小老鼠163.com, 欢迎交流