Lpm_divide仿真正确,硬件结果不正确

时间:10-02

整理:3721RD

点击:

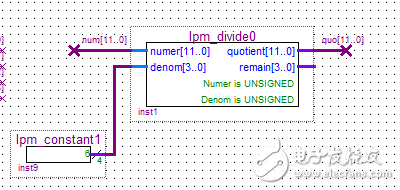

小弟最近需要做一个除法器,使用洪模块LPM_divide, 在仿真正确但结果不正确,想问一下问题出在哪里? 电路图如下:

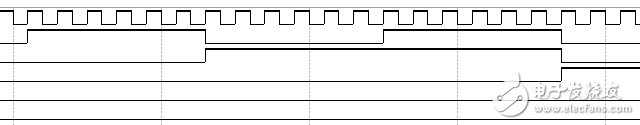

除数是一个常数6,仿真图如下:

除数是一个常数6,仿真图如下:

可以看到每六个上升沿会变化一下,但在硬件上遇到了问题,无论怎么改变除数,输出结果都是除以2(除数为2),特别困惑想问一下是什么问题?

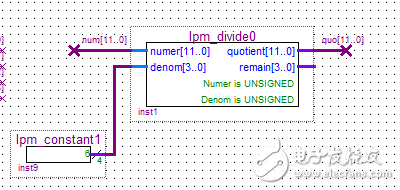

除数是一个常数6,仿真图如下:

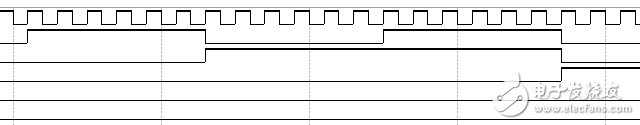

除数是一个常数6,仿真图如下:

可以看到每六个上升沿会变化一下,但在硬件上遇到了问题,无论怎么改变除数,输出结果都是除以2(除数为2),特别困惑想问一下是什么问题?

是不是输入的频率太高了

改变除数后有没有更新lpm_constant1模块,要是没有更新的话,还是原来的数据