Quartus13+Modelsim仿真testbench应该怎么写呢?菜鸟已经吐血了

时间:10-02

整理:3721RD

点击:

在Quartus中写了一个非常简单的分频器module testdiv(mclk, out),编译OK,quartus生成testbench模板如下,在always块加入时钟产生语句,out=~out;如下

才接触Modlesim,折腾好久了,真心不知道该怎么搞了,求大大们拯救啊

我是菜鸟

- `timescale 1 ps/ 1 ps

- module testdiv_vlg_tst();

- // constants

- // general purpose registers

- reg eachvec;

- // test vector input registers

- reg mclk;

- // wires

- wire out;

- // assign statements (if any)

- testdiv i1 (

- // port map - connection between master ports and signals/registers

- .mclk(mclk),

- .out(out)

- );

- initial

- begin

- // code that executes only once

- // insert code here --> begin

-

- // --> end

- $display("Running testbench");

- end

- always

- // optional sensitivity list

- // @(event1 or event2 or .... eventn)

- begin

- // code executes for every event on sensitivity list

- // insert code here --> begin

- # 10 mclk=~mclk ;

- @eachvec;

- // --> end

- end

- endmodule

才接触Modlesim,折腾好久了,真心不知道该怎么搞了,求大大们拯救啊

我是菜鸟

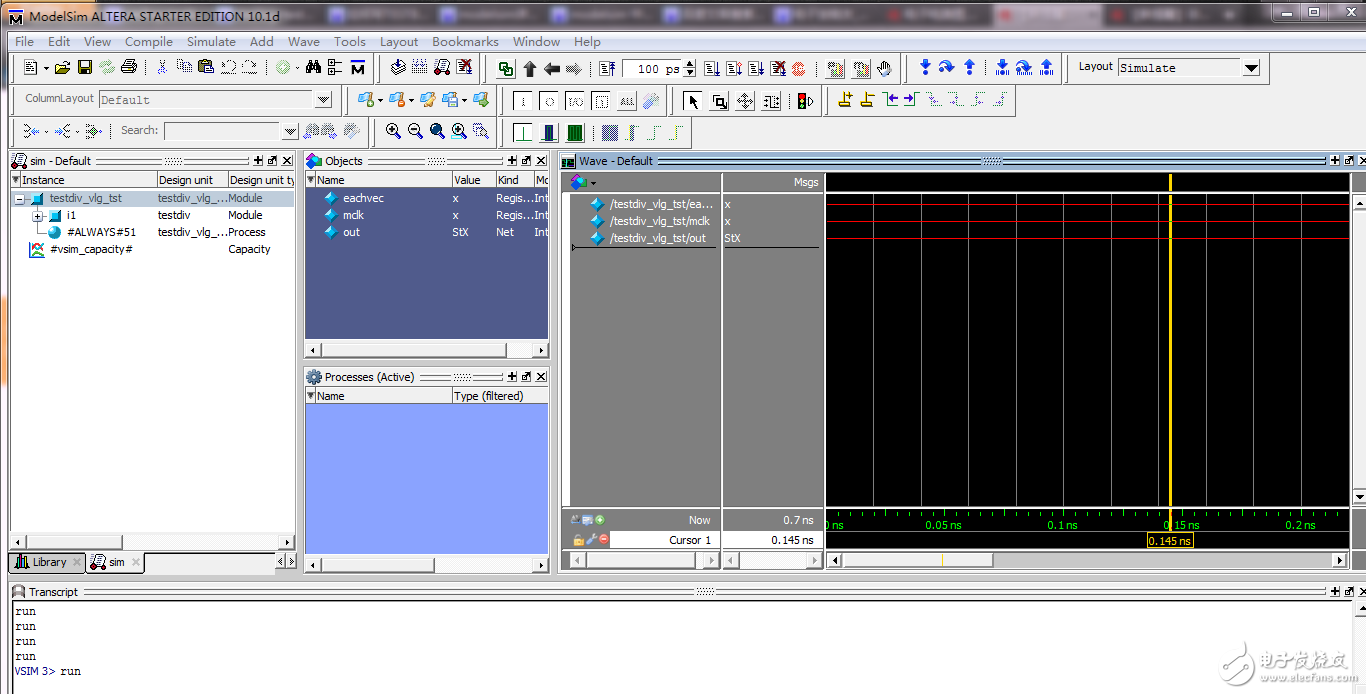

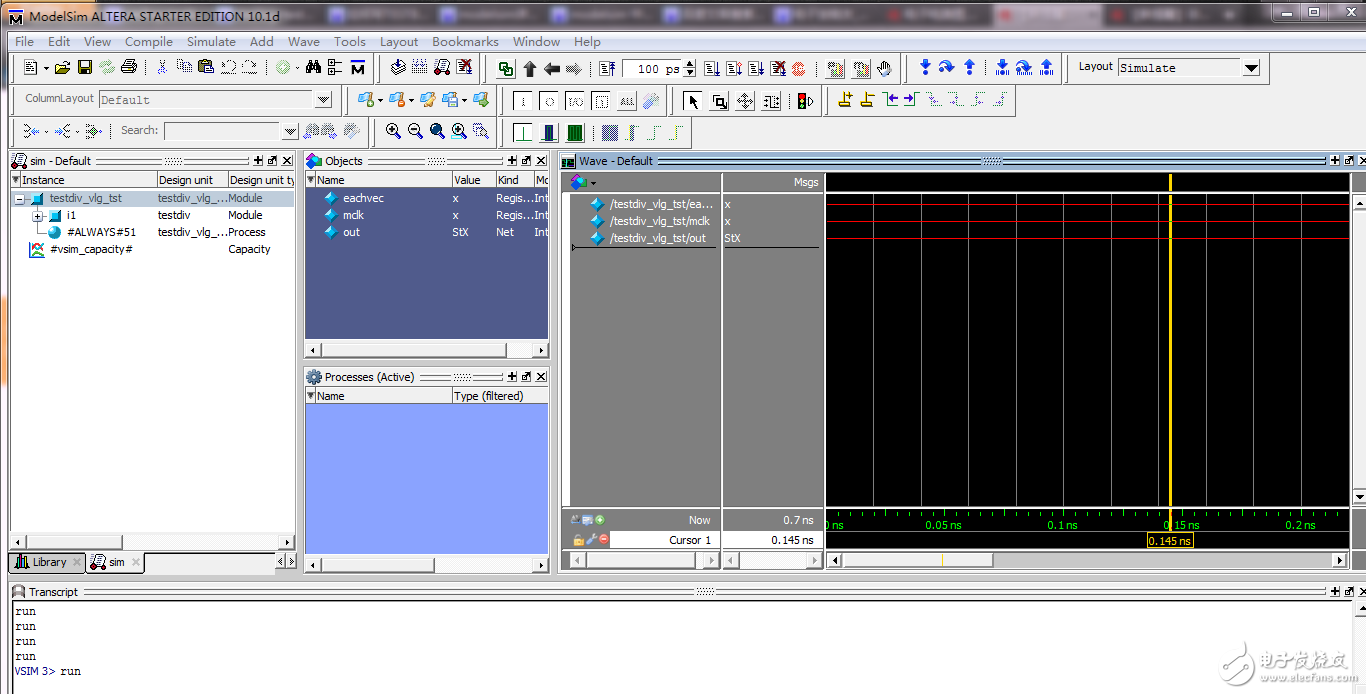

在initial块里添加了mclk的初始化语句,mclk=0,然后mclk可以显示波形了,但是输出仍然没有波形,该怎么办,大大们,求解救

大大们不给力啊,问题原因找到了,reg没有初始化,所有的reg都要在initial里面初始化,不然modlesim就划定为未知状态而没有波形,代码不严谨啊,花一天买了一个教训