McBSP_I2S通信(1)

我的项目拟采用I2S通信方式实现ADC与McBSP之间的数据传输,所以接下来我将采用I2S通信方式尝试调试6748的McBSP模块。如有错误,请大家帮忙指出,遇到不懂的还希望大神指点一二!

1、I2S通信简介:

I2S(Inter—IC Sound)总线,又称集成电路内置音频总线,是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专责于音频设备之间的数据传输,广泛应用于各种多媒体系统。它采用了沿独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。

I2S有3+1个主要信号:

(1)、串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数。

(2)、帧时钟LRCK,(也称WS),用于切换左右声道的数据。LRCK为“1”表示正在传输的是右声道的数据,为“0”则表示正在传输的是左声道的数据。LRCK的频率等于采样频率。

(3)、串行数据SDATA,就是用二进制补码表示的音频数据。

(4)、有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍。

2、McBSP模块简介:

多通道缓存串行端口(McBSP)主要用于音频接口。这款McBSP 是一款用于其它TI DSP 上的 McBSP 外设的专业版本。主要音频模式支持AC97 和I2S 模式。除了主要音频模式,McBSP 可以编程为支持其他串行格式,但不用作高速接口。McBSP 包括一个数据通道和一个连接到外部设备的的控制通道。独立引脚是为了传输和接收这些外部设备的通信数据。CPU 与McBSP 之间的通信是采用可通过内部外围总线访问的32位控制寄存器的方式。

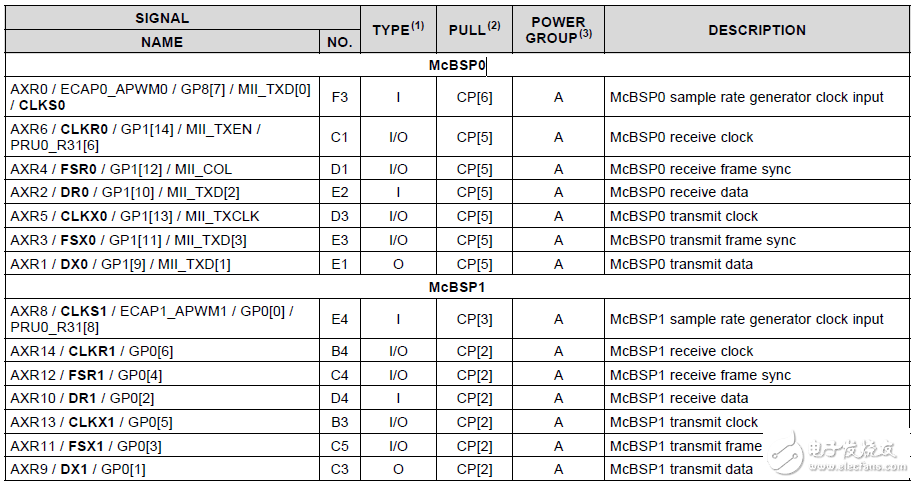

6748DSP包含2个McBSP,即McBSP0和McBSP1。引脚分布如下:

3、硬件连接:

ADC通过I2S方式与McBSP相连,ADC发送数据,为主机;McBSP接收数据,为从机。硬件连接如下:

ADC_ BCLK————————————McBSP0_ CLKR0;

ADC_ LRCK————————————McBSP0_ FSR0;

ADC_ SDATA————————————McBSP0_ DR0;

ADC_ MCLK————————————McBSP0_ CLKS0;

4、软件调试:

未完,待续……

你测试完成了吗?我也在做C6748采集AD的程序呢,可以交流一下吗?我的QQ496603471

很快也要用6748的MCBSP调音频了,先顶一下

请问你有OK的代码吗,可以私聊,QQ2471276661

我也搞到了板子哦

昨天刚拿到手啊,

还没开始玩,向小编学习