+ 定时器

时间:10-02

整理:3721RD

点击:

Timer Plus

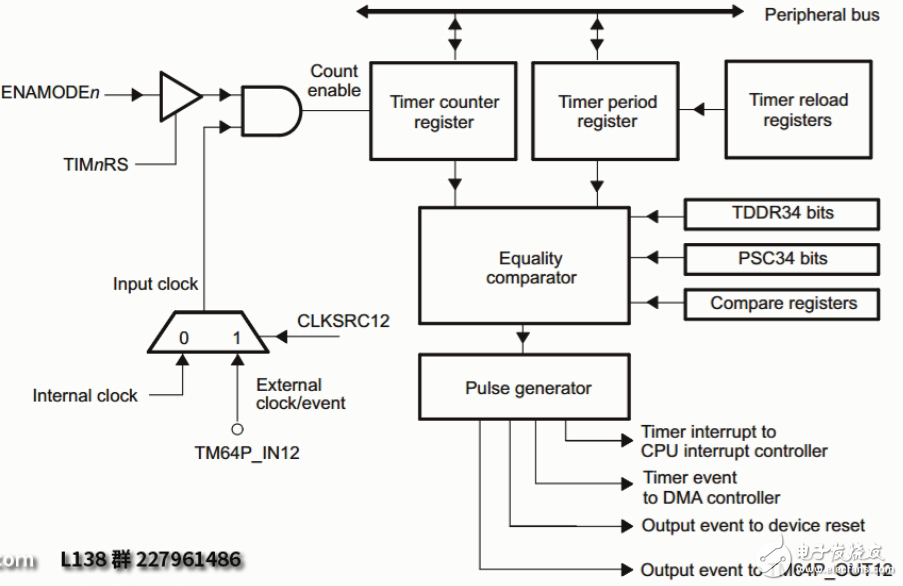

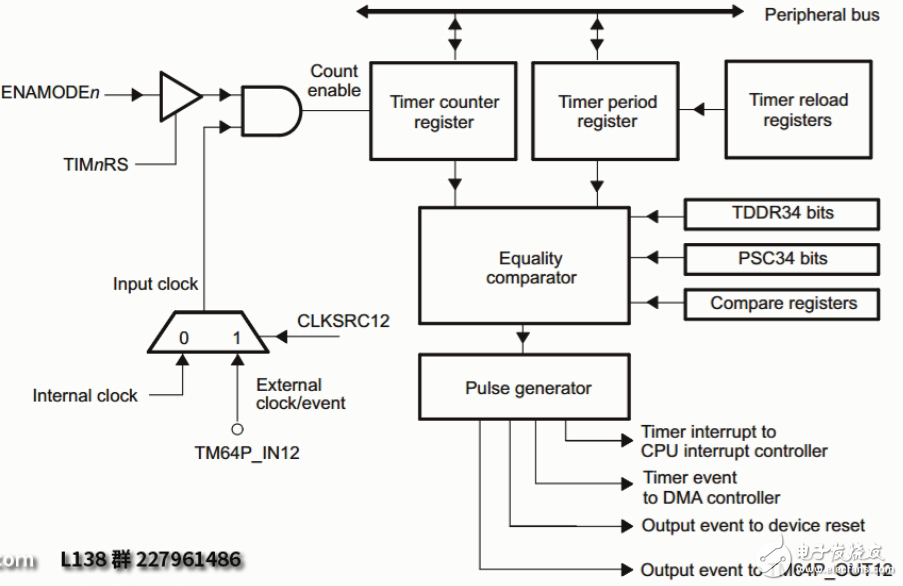

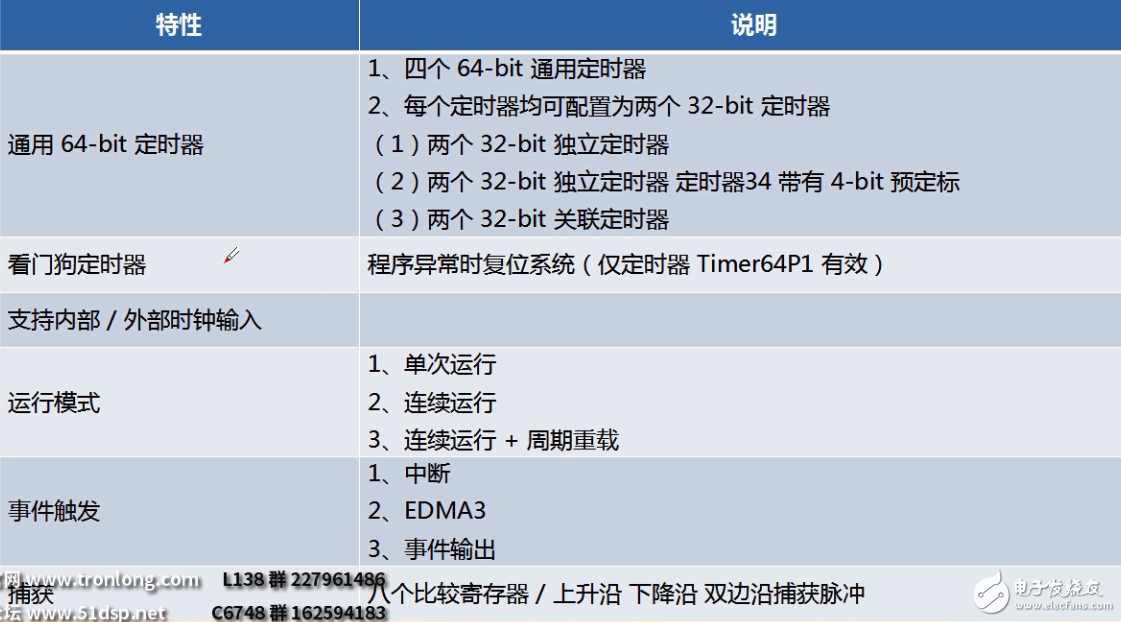

最简单的外设之一

时钟:内部锁相环/外部时钟(计数器)或事件

模式选择:单次运行,连续运行,连续运行+周期重载

运行过程中的操作:定时器计数寄存器,时钟脉冲来,+1

比较模块产生脉冲,生成四个事件:

1.产生CPU中断到CPU控制器

2.DMA事件到DMA控制器

3.复位CPU,POR(power on reset),将CPU所有外设、核心等所有设备复位。事件由看门狗定时器来产生,只能将定时器一来作为看门狗定时器。

4.输出事件到输出管脚(脉冲信号)

下面是概述图:

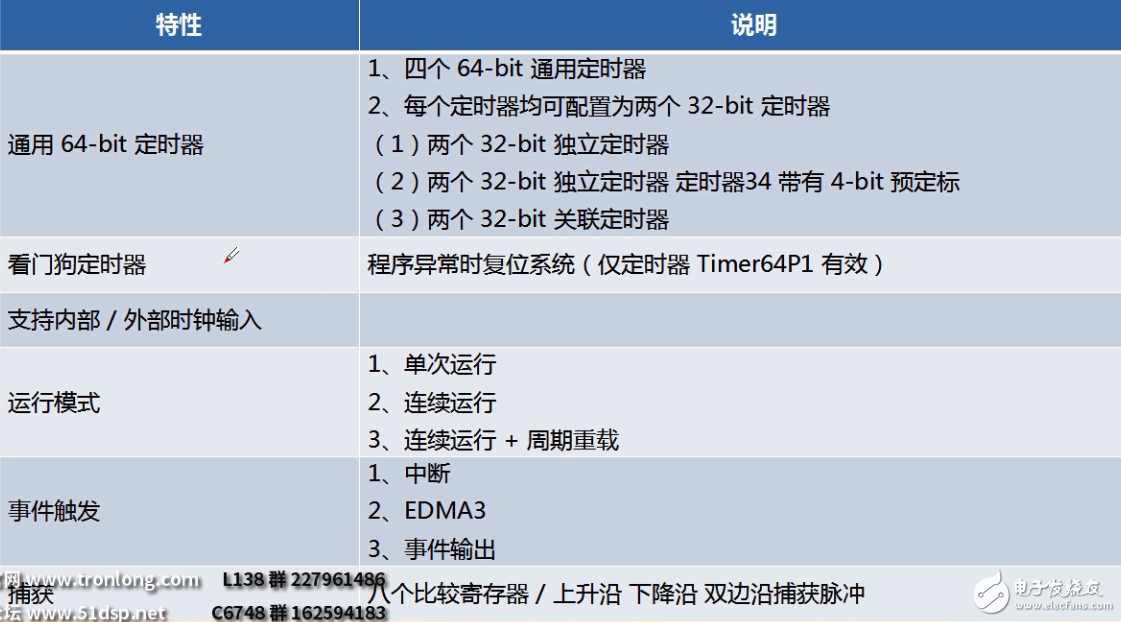

C6748 64位寄存器,低32位定时器叫定时器一二,高32位定时器三四。

定时器三四可以指定分频系数

配置为关联定时器:定时器三四作为定时器一二的预定标,即预分频

与八个比较寄存器比较产生相应事件

定时器一二,PLL旁路时钟

定时器三四,默认都使用PLL0_SYSCLK2时钟,CPU二分频

为什么外设时钟频率可选?

答:降CPU频降功率;但串口、定时器等需要稳定的频率。PLL1与CPU无关的锁相环,就使用固定的频率运行。

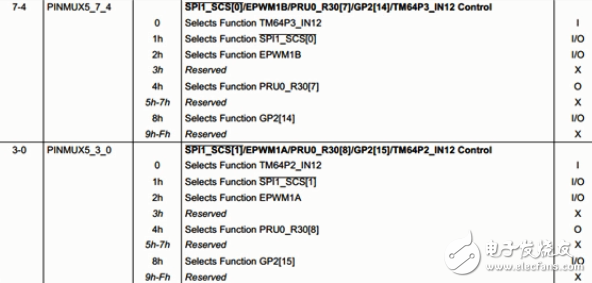

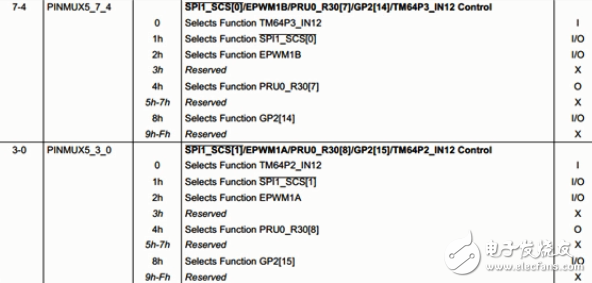

下图为定时器三四输入、输出管脚

时钟输入管脚(默认配置)

时钟输出管脚(必须重新配置)

定时器一二:时钟输入输出管脚为同一个管脚

最简单的外设之一

时钟:内部锁相环/外部时钟(计数器)或事件

模式选择:单次运行,连续运行,连续运行+周期重载

运行过程中的操作:定时器计数寄存器,时钟脉冲来,+1

比较模块产生脉冲,生成四个事件:

1.产生CPU中断到CPU控制器

2.DMA事件到DMA控制器

3.复位CPU,POR(power on reset),将CPU所有外设、核心等所有设备复位。事件由看门狗定时器来产生,只能将定时器一来作为看门狗定时器。

4.输出事件到输出管脚(脉冲信号)

周期重载寄存器:改变定时器每次计数达到最大值时所要重载的值

作用:比如输出PWM波时,通过改变重载的值,就可以输出不同的PWM波形

下面是概述图:

C6748 64位寄存器,低32位定时器叫定时器一二,高32位定时器三四。

定时器三四可以指定分频系数

配置为关联定时器:定时器三四作为定时器一二的预定标,即预分频

与八个比较寄存器比较产生相应事件

定时器一二,PLL旁路时钟

定时器三四,默认都使用PLL0_SYSCLK2时钟,CPU二分频

为什么外设时钟频率可选?

答:降CPU频降功率;但串口、定时器等需要稳定的频率。PLL1与CPU无关的锁相环,就使用固定的频率运行。

下图为定时器三四输入、输出管脚

时钟输入管脚(默认配置)

时钟输出管脚(必须重新配置)

定时器一二:时钟输入输出管脚为同一个管脚

不错的样子,顶,学习中!

不错的