基础(二):电路分析

可能我的cadence16.5与创龙用的16.5的补丁版本不一样,所以我打开PCB时,有一些问题,一些元件不能移动,还有一些显示上的不同。不过不影响分析。

一、原理图

这里就对一些主要的内容时行分析,一些普遍的就略过了。

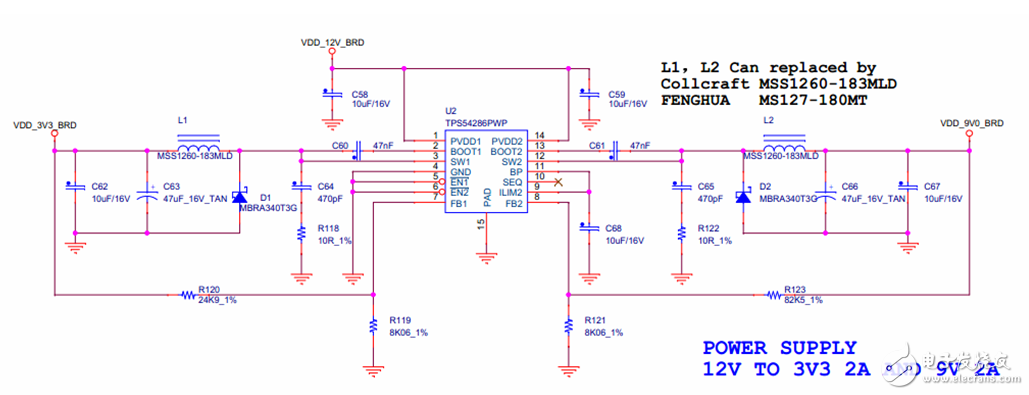

1、电源芯片采样的是TPS54286,将12V电压转为3.3V与9.0V

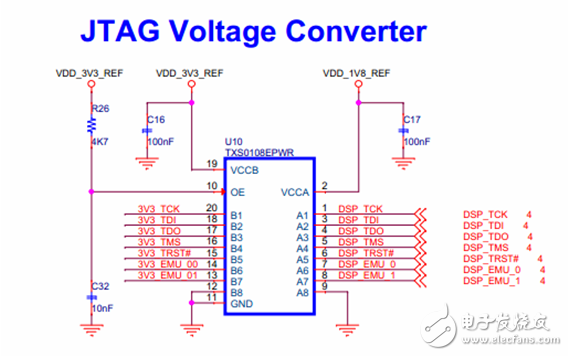

2、电路主要都是一些接口,值得学习的是,串口部分加了变换器,对DSP进行了保护。

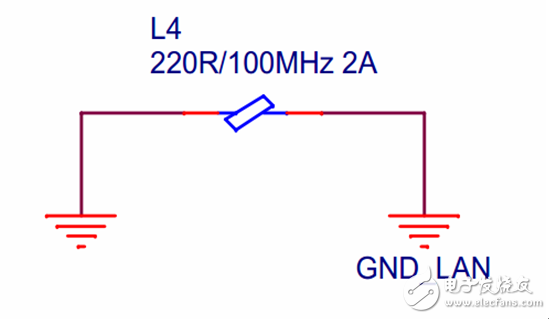

3、网口这里,接口的金属壳体与地之前只是接了一个磁珠,不清楚这相的防护是不是够,一般我们做的时候加了压敏啊,电容啊什么的好多呢。

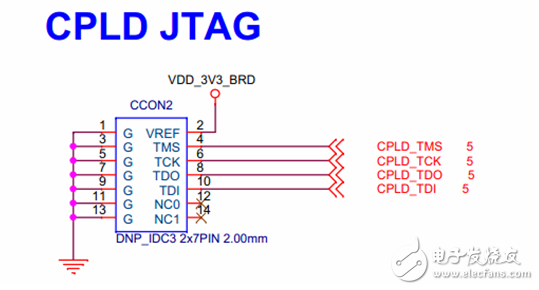

4、还有一部分是CPLD的JTAG,好像没有看到CPLD啊,核心板上好像也没有,这个是兼容其他型号核心板的吧。

5、由于芯片电压是1.8V的,所以仿真接口要从3.3V转换到1.8V的。

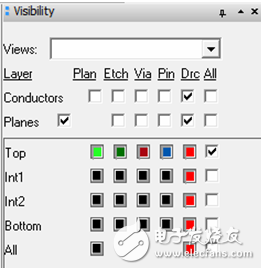

二、PCB板图1、底板的PCB采样四层电路第一层为布线层,覆铜有GND与电源。第二层大部分是GND,有电源1.8V、2.5V等电源层第三层全是GND层。第四层为布线层,覆铜也是有GND与电源。 两层内电层中通常上会设置一个GND层一个VCC层,而两层中都有大面积的覆地,对于抗干扰应该是很有帮助的。

PCB布线整体显示,布线上还是很规整的。

2、PICe接口部分,可以看到地线布线部分都是有两个过孔。

3、SRIO部分,这一部分就是很多的差分线,

4、千兆网口,可以看到网口与我们平时用的网口有所不同,有四对差分线。

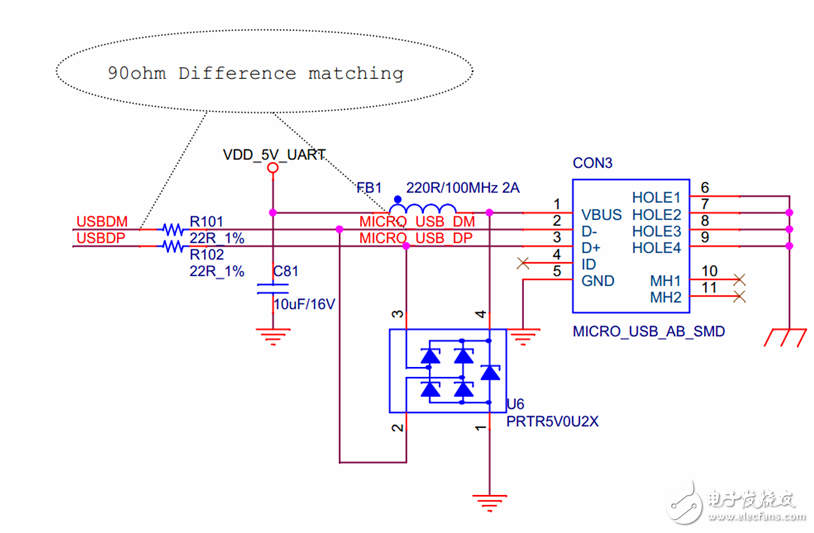

5、差分线的规则设置:

在原理图中也相应的标示出了差分线:

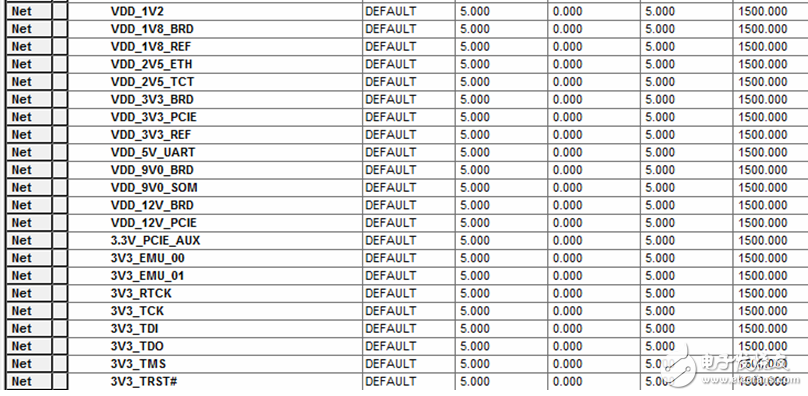

但在规则中电源线的布线宽度也设置成了5mil,在PCB上虽然布线时布的加粗了,但这个设置不免会有遗漏。

CPLD是在核心板背面,赛灵思的XC2C64A。

没细看手册,手册上说那是EEPROM

这个CPLD偶也是听说没有了解过,兄台可以了解一下,看跟FPGA有什么差别。我也是之前看过C665x的规格书才知道的

资料里没有这个CPLD的说明,怕是里面有程序或是什么验证之类的,私自烧了程序怕是对核心板有影响。

CPLD 里面是上电复位时序和一些控制信号 改写程序后核心板 DSP 就不能启动了

并不开放吧。

明白了,那就不动了。

是啊 所以底板 CPLD JTAG 口默认不贴

分析得很好!值得学习学习!~

你好,我在学习DSP。这个板子的原理图文件能不能分享一份给我?谢谢!