C66程序优化注意事项

C66x DSP是TI最新出的定点和浮点混合DSP,后向兼容C64x+和C67x+、C674x系列DSP。本文不介绍C66x构架,不炫耀定点DSP的浮点和定点处理能力的增强,以及C66x新引入功能。重点介绍,算法移植工程可能遇到问问题:

分几个专题:

- 平台配置

- cache使用

- 芯片级程序优化

- 程序级优化

- 算法级优化

平台配置66ak存储资源结构:

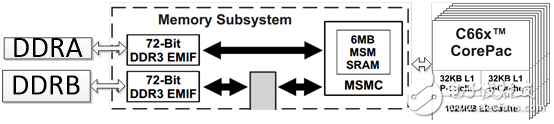

存储资源包括DDRA、DDRB,共享内存MSMC,每个核的局部L2、L1P、L1D。由于整个芯片的地址空间是物理统一编址的。L1,L2运行时钟为主频,常规64系列L2运行时钟为主频一半。MSMSRAM 运行在主频。DSP core直接读取L1,L2,通过MSMC读取SRAM,外部DDRA。

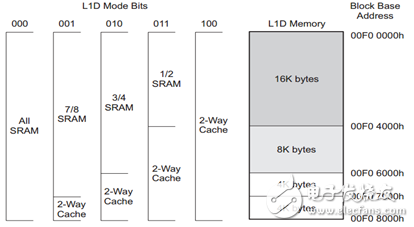

L1P可配置程序缓存;L1D可配置数据一级缓存,2-Way Cache;L2可配置数据二级缓存,4-Way Cache。缓存区域从高地址开始分配。如下图:

程序数据存放区域分类

程序存放区域:用于存放所有可以执行的代码和常量,程序运行过程中,不会发生改变;

数据存放区域:用于全局变量和局部变量保留的空间,程序运行过程中会发生改变;

堆栈存放区域:为系统堆栈保留的空间,用于和函数传递变量或为局部变量分配空间。若因意外改变,会导致程序跑飞。

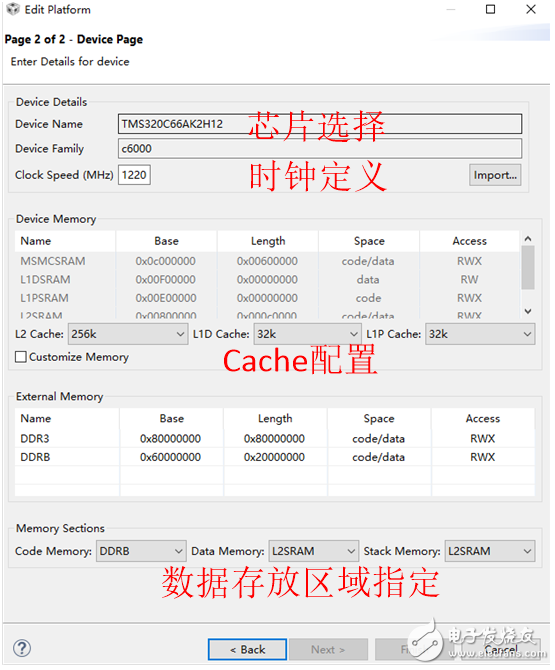

平台配置通过新建或修改Platform文件来实现存储资源定义,Cache大小分配,及程序数据存放区域指定。以66ak12为例,缓存区域L1P,L1D全部设置为缓存,L2缓存大小设置为256k。程序存放于DDRB,数据存放于L2,堆栈存放于L2进行。配置过程如下:

Debug模式下,选择tools -> RTSC Tools -> Platform -> New,根据自己的需要选择Platform保存的路径以及对应的芯片,Next,填入所需要的各种空间的大小和起始位置。

平台调用及验证

调用Platform:

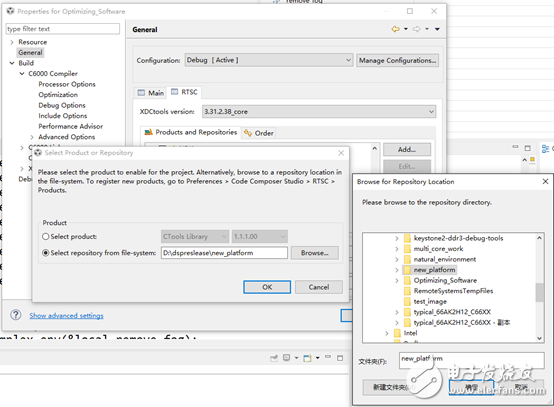

在工程查看窗口,相应工程上右键Properties,选择General -> RTSC,找到最后一项,Other Repositories,点击Add,路径选择上一步保存的路径,需要注意选择XDCtools版本,然后就能找到自己新建的Platform

验证:

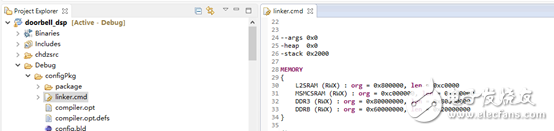

查看通过自动生成CMD文件查看,如下图所示,L2SRAM大小为768K。详细程序数据存放位置通过map文件查看。程序调试过程中,通过ROV也能查看堆栈大小。

注意事项

1. 多核同时运行时,必须保证数据段,堆栈存放位置不重叠。多核共享变量除外。

2. 多核共用一个程序,程序区域位置可重叠,多核采用不同程序,程序存放区域也不能重叠。

未在平台配置文件中定义的区域,如不定义DDRA空间,也能通过绝对地址访问。

cache大小配置

平台配置

平台加载

平台验证