McBSP_I2S通信(3)

时间:10-02

整理:3721RD

点击:

上一篇帖子所述问题已经得到解决,如果有朋友在做相关方面的研究,我的经验可以提供些许参考,所以整理出这个帖子。

I2S通信有三根时钟信号线,分别为主时钟SCLK、帧同步(左右通道选择)时钟LRCK、位时钟BCLK。由I2S通信原理可知:

SCLK的频率=采样频率的256倍或384倍;

LRCK的频率=采样频率;

BCLK的频率=2*采样频率*采样位数。

我所选择ADC的实际情况为:

SCLK的频率=384*采样频率;

LRCK的频率=采样频率;

BCLK的频率=2*采样频率*32。

ADC为主设备,由外部输入主时钟,并产生帧同步信号以及位时钟信号。由DSP的PLL0_SYSCLK5进行25分频产生18.24MHz频率的时钟信号,将其作为SCLK输入ADC。根据公式SCLK的频率=384*采样频率,可知:采样率=47.5KHz;LRCK的频率=47.5KHz;BCLK的频率=3.04MHz。

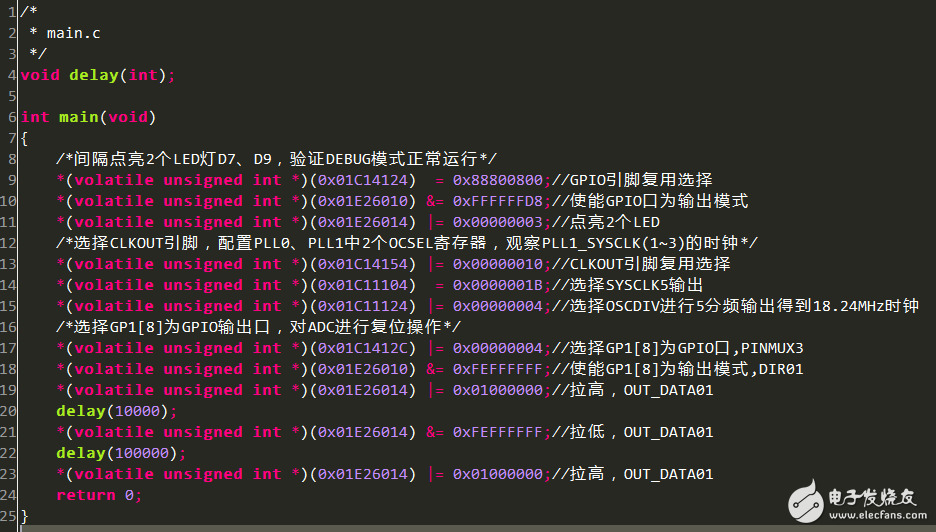

此外ADC还需进行复位操作,所以将开发板上引出的引脚J3_1(即GP1[8])配置成GPIO口,并设置为输出口,连接ADC复位引脚(低电平复位)。对ADC进行复位操作:GP1[8]拉高、延时;拉低、延时;再拉高。配置程序如下:

还要补充一点就是我修改了GEL文件直接配置PLL0_SYSCLK5;

此外,GPIO口的配置是直接对寄存器进行操作,延时也是自己编写的,程序太随意,这些做法是不严谨的!

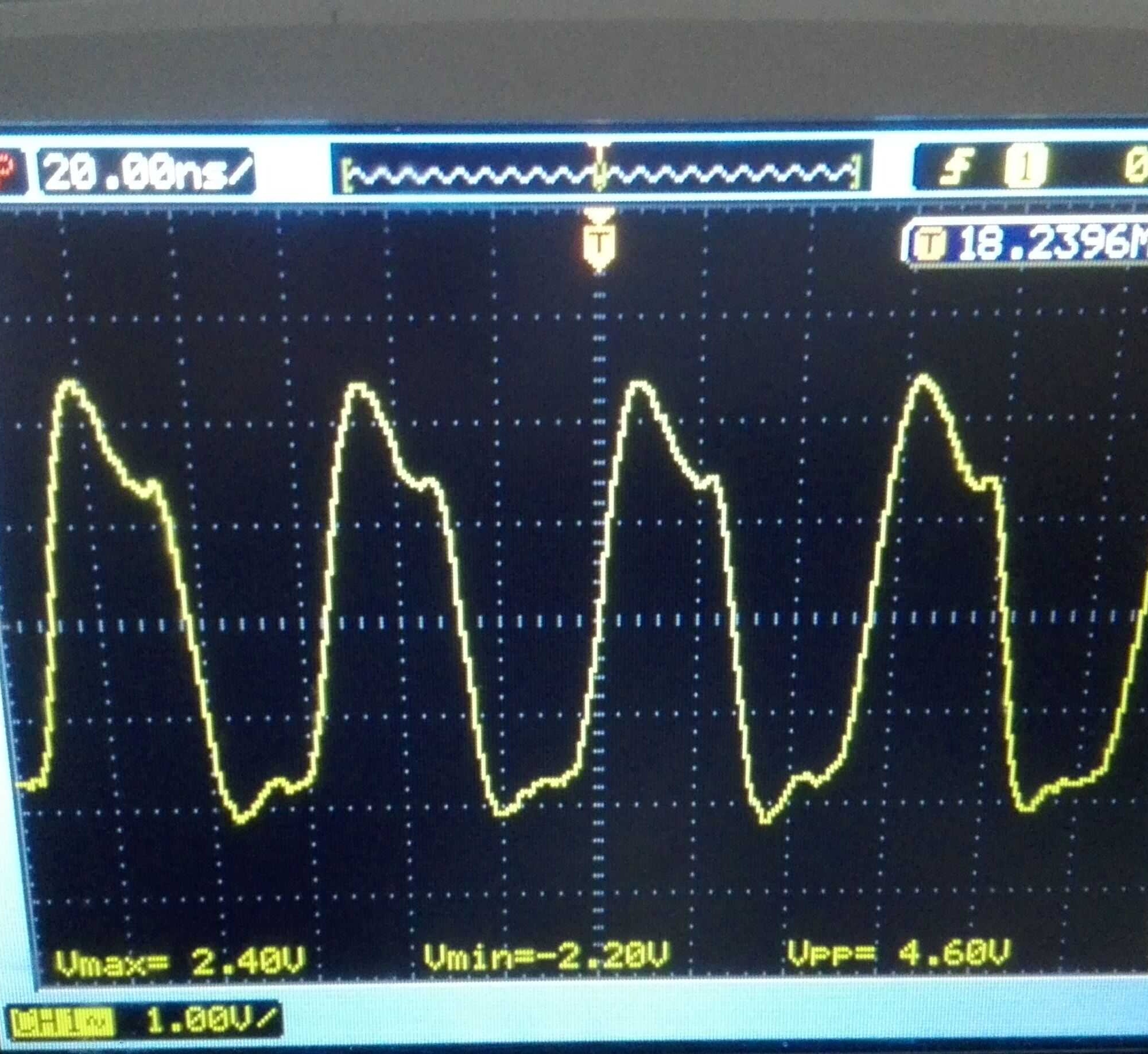

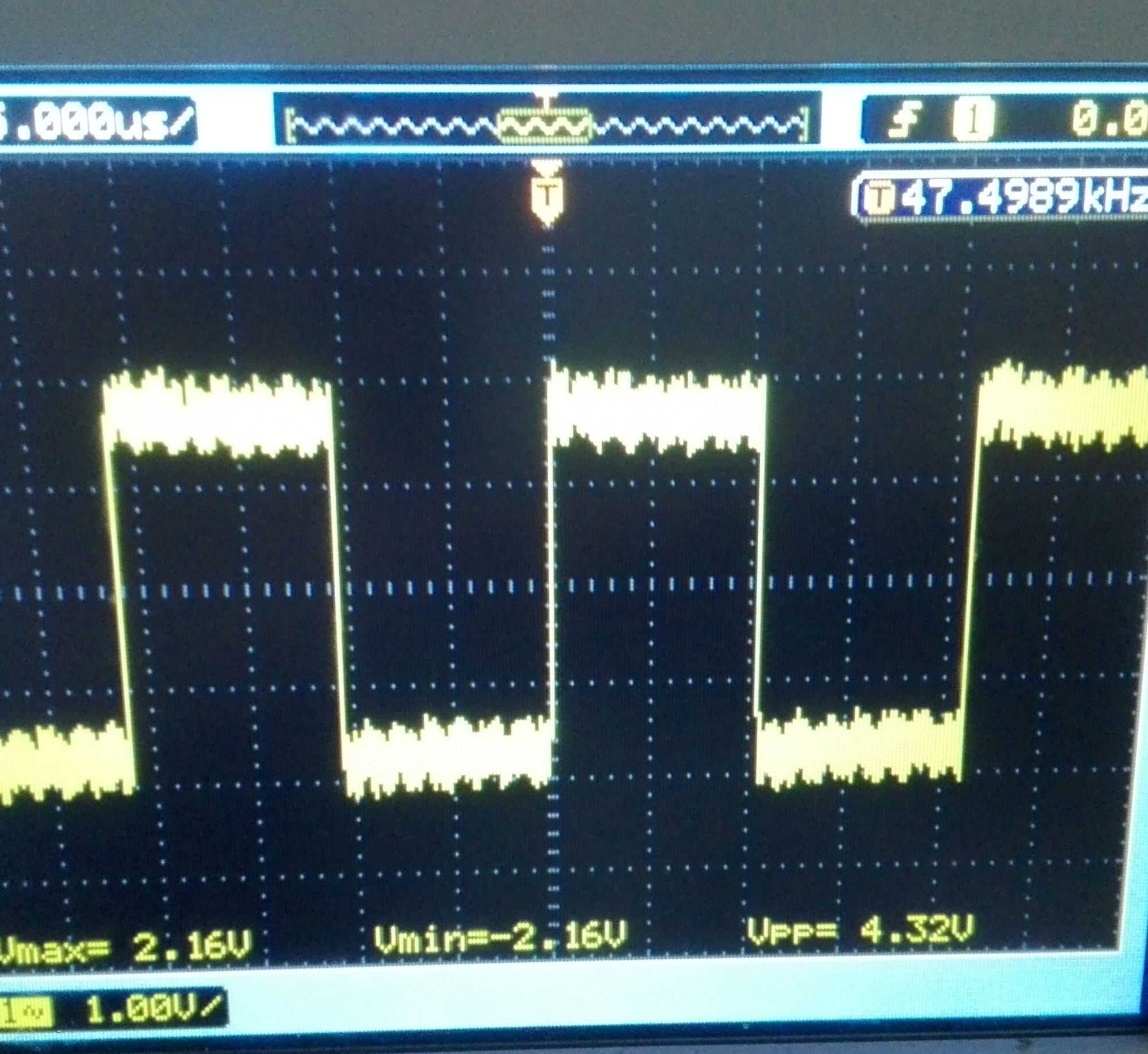

幸好结果还是正确的,这是实际测量的三个时钟信号,与理论值相符:

1、SCLK=18.24MHz

2、LRCK=47.5KHz

3、BCLK=3.04MHz

严重怀疑你这个示波器是不是有问题,校准一下。

OK,校准一下试试!