+64位定时器的应用

时间:10-02

整理:3721RD

点击:

定时器的作用就不多说了。c6748这款芯片有四个64位定时器,可以说是资源丰富,下面就简单说一下。

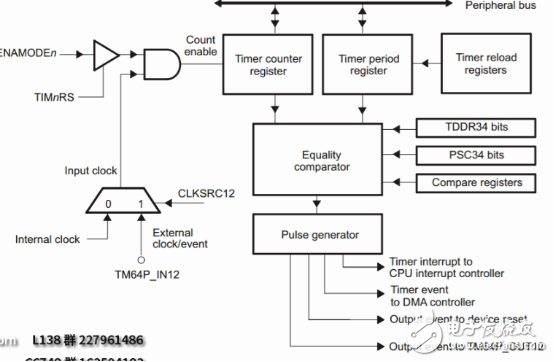

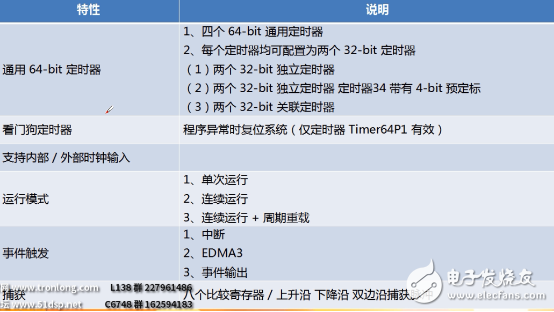

由上图可知,c6748的输入时钟既可以是内部时钟也可以是外部时钟或者是外部事件。外部事件就是EDMA,中断等。后边程序的执行就会根据使用的时钟周期进行定时或者是计数,并与设定值进行比较,产生脉冲触发事件。触发的事件有CPU中断,dma中断,复位中断(全部复位操作),输出事件到相应管脚的脉冲。顺便说一下上图中的TDDR34和PSC34.这些其实是指当64位定时器分成两个独立32位定时器时,低32位所对应的定时器。下图可以十分清楚的展示c3748的4个64位定时器的特性:

对于c6748的四个定时器其中P0和P1所用的时钟位PLL的旁路时钟,时钟周期为24M,而P2,P3所用的时钟为PLL_SYSCLK2,时钟周期为228M。但是为什么要这样设置,而不直接使用CPU的时钟呢,因为c6748是一款低功耗的芯片,所以为了节能他的CPU的频率可能随时 发生改变,如果所有的定时器或者是外设都依赖于CPU的时钟周期则会造成定时不准等问题的发生,所以为了不影响其他外设的功能,就将他们分开处理。

还有一点注意一下,c6748的定时器0和定时器1的输入输出引脚为同一个,不能同时实现输入和输出,如果一定要这样的话,可以试试分时复用。对于定时器各种工作模式在此就不多数,光盘上的历程中都有详细的代码,配置过程答题类似。