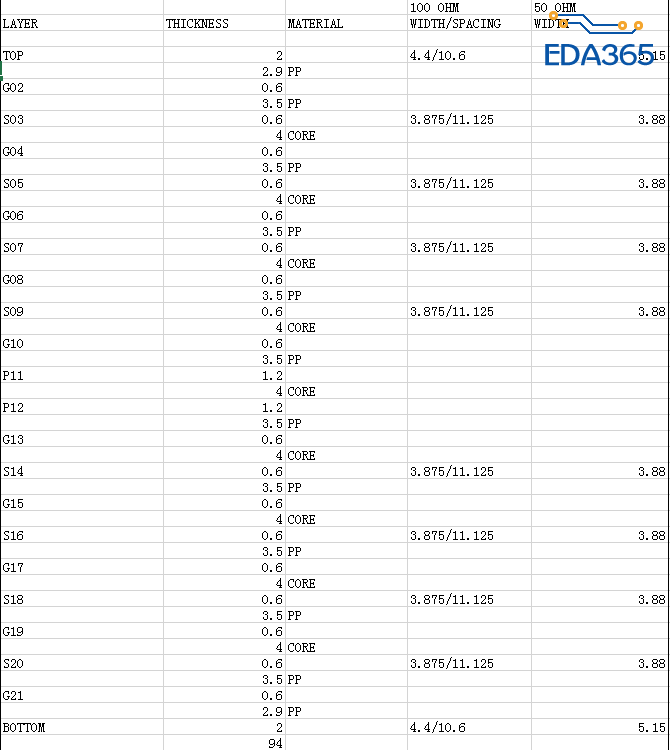

自己叠了个22层板 板厂说不合理 请高手指正

不合理能具体点吗?过于笼统不好分析

就说不合理,我也搞不清楚。22层 2.2mm厚的板子 叠层顺序就是上面的那样,你能看出来哪不好吗?

是不是我的top和g02 g02和g03之间都用的pp的问题?应该是top和g02之间pp然后依次是core-pp-core这样下去 到最后g21和bottom之间用pp?

一般的常规板子的压合是不是应该只有top bottom用pp 中间的都是core-pp-core这样的?例如上面的22层的 对称的板子 中间两层电源

走线太细,间距太开,差分线都快赶上单端了

确实有一些不符合常规。如果不是HDI板的话,一般G02到S03使用的是core,这样比较方便些。至于其他的应该问题都不大。另外有可能是楼上讲的,你问的板厂做不了这个板子

那判定差分还是单端是不是应该有个标准,比如间距大于多少,或线宽的范围?

常规的做法是不是top bot用的是pp 其他都是core 然后用pp连在一起?

间距大,差分线的耦合很弱了,线宽这么细,阻抗会差得很。 线宽这么细,损耗也非常大。标准倒没有看到, 还有 PP在上下层,还要买铜泊。

没错,确实如你所说,但是你现在的却不是那样的

非常感谢!

确实感觉这个线宽和线距,在当前的叠层下无法达到100欧的阻抗,大概也就80欧左右吧

你们都是polar算的吗?

恩,是的,即便用3.8的介电常数这个阻抗还是到不了90欧。

当然了,如果只有G02作为参考曾,G04不作为参考的话倒是有可能达到100欧左右

只参考g02不参考g04有100欧姆这个是理论值吗?只是计算的时候选择不同的模型?

例如下图这种?能不能把你计算的模型和数值截图看看,只参考g02的和两面都参考的这两种的。

板子上实际的情况哪条线的阻抗是多少不应该是一个固定的值吗?信号线不是和他的上下面都会有关系的吗?