封装设计不慎引起的问题

时间:10-02

整理:3721RD

点击:

封装设计不慎引起的问题

昨天接到smt工厂端反馈器件坐标文件和实际文件不符的问题,调入Pcb后发现是由于封装设计引起的问题(Protel设计软件)。详见下面:

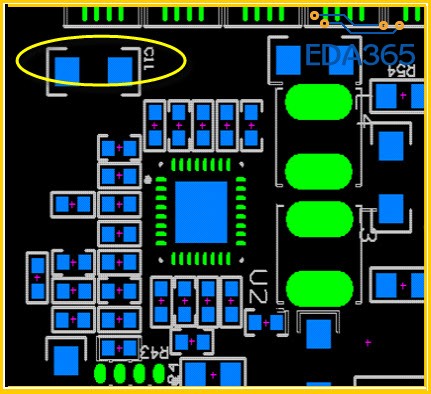

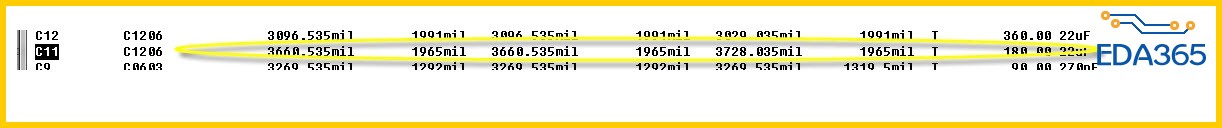

1,smt工厂反馈的图。从图中看显示C11器件是在顶层

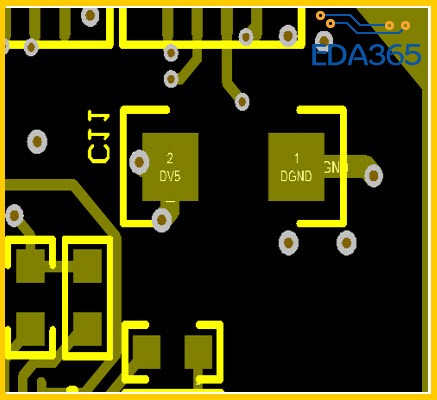

2,打开PCB中查找到C11,器件实际在底层

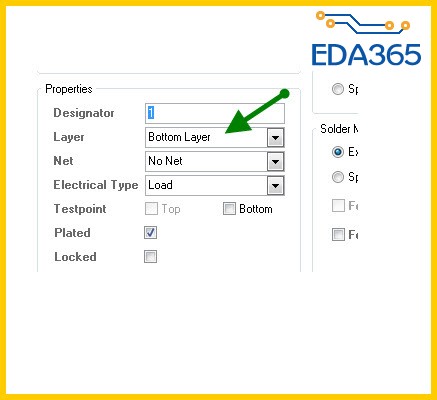

3,封装焊盘,显示焊盘作在了底层

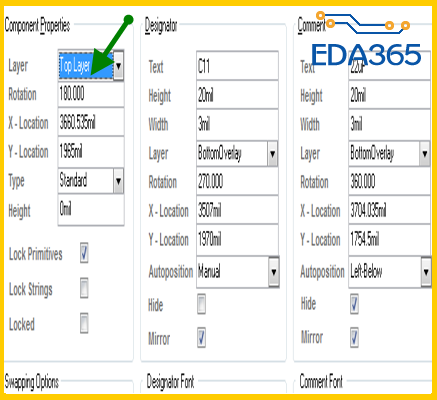

4,器件属性中显示器件在顶层,实际在底层

5,坐标文件显示器件顶层,坐标位置正确。但由于层面错,导致smt软件输入后镜像,坐标文件和实际文件就不一致了。

大家在用protel设计时要当心,有些封装等东西在软件中不严谨,容易出问题。

又学习了,有时候Layout时误操作软件也会出现器件在顶层(底层)其丝印却在丝印底层(丝印顶层)的现象

出完GERBER自己再检查检查咯

这个软件木有用过,查看GERBER文件要仔细

处处小心啊

细节很重要~~

这个真得细心了,特别是板子大这种问题很难发现。

这么大的bug,布线时候没有发现:L:L:L

出完GERBER是检查不到了 只有pcb中才好查看

布线时都着急布通线了,这种问题很容易忽略。只有作封装时要慎重和检查。

不能说Protel不严谨,像这种错是做封装的马虎,用其它软件一样也能做出这样的封装而且不报错!

对,这种根本与软件无关,纯粹是操作的人水平太差。这种事都做的出来。

这问题很早就发现了并注意规避了 !这个是作封装的人不注意或者乱来...见过有些丝印是顶层,焊盘在底层,元件属性显示在顶层的封装