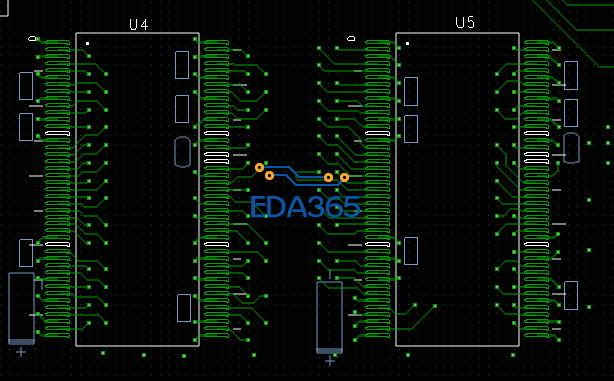

SDRAM 扇出问题

手动扇出,养成设置大格点的习惯就OK了,12.5或者25的格点,打孔打到格点上。

应该是先拉出线来,再打孔吧 不拉线的话,via打不出来呀?

所谓的扇出,就是从焊盘拉一段线、打孔的操作。

哦,明白了 ,谢谢呀

还有一个问题,外层差分阻抗共面地模型在什么情况下使用,它跟外层差分阻抗模型区别是什么?现在画板子都很喜欢大面积的覆铜,信号层也是这样,比如说一个四层板,L1、L4为信号层,L2为GND,L3为VCC,布完线后L1、L4会大面积的覆铜,然后会打许多的地孔。L1、L4上走100欧姆的差分阻抗线,我想问我是用Edge-coupled Coated Microstrip 1B(外层差分阻抗模型)模型还是用Diff Coated Coplanar Stirps with Ground 1B模型(外层共面差分阻抗)呢?个人觉得通过大面积铺地应该是属于共面的阻抗,期待回复……

如果你只参考平面层去做阻抗计算,算不出你想要的阻抗值时,可以考虑用共面阻抗的模型。两种模型没什么太大区别,具体用哪种取决于你的线宽、线间距、介质厚度等等参数能否计算出你想要的阻抗值。

通常共面阻抗模型在双面板用的比较多,因为双面板通常很难保证有一层完整的参考平面。

至于表底层大面积铺地,这种处理是好的,但是注意铺地要离走线距离尽量大于25mil。因为铺地离走线25mil以上,就对走线的阻抗影响非常非常小了。当然前提是你的走线离内层参考平面距离较近。

建议自己在si9000软件里模拟一下,在共面阻抗模型下,你先把共面的铺地跟走线的距离设置为8mil,然后逐渐增大,观察一下阻抗值的变化,应该可以大概得到一个规律。

以上是我个人看法,仅供参考。

好的,谢谢你,我试试

什么都是手动 fanout 好.