请教:POWER DC中最佳感应线是什么?

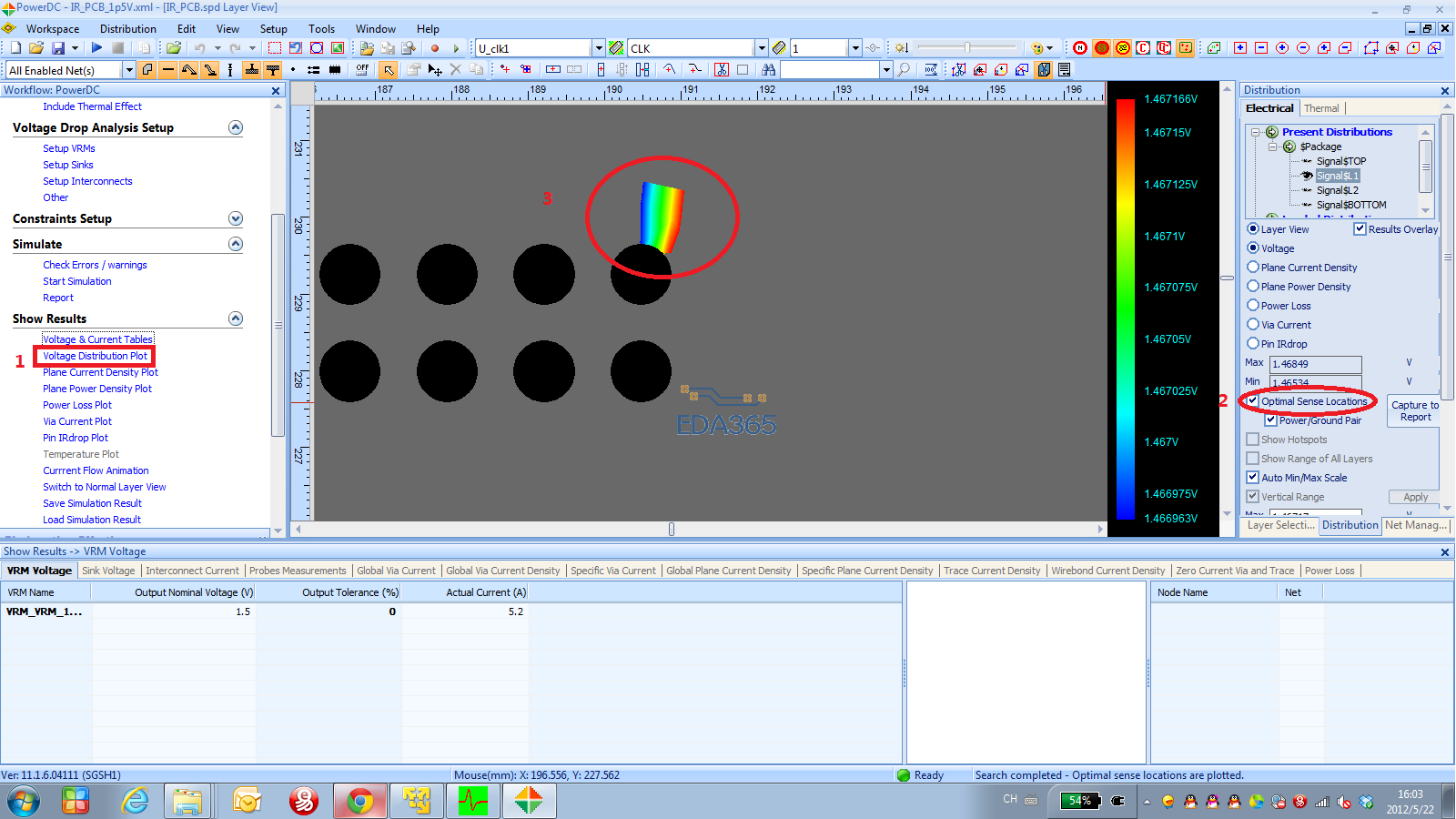

再补充一下,POWERDC仿真完成后,点击IR Drop Analysis仿真流程,在show results结果中,选择voltage distribution plot后,

右边窗口的distribution标签中,勾选optimal sense locations,这样软件就可以自动计算出感应线。

当然你的VRM必须要有sense pin才有用。通过在感应线上打一个过孔,通过连线,接到sense pin。

刚接触,请高手扫扫盲

现在很多VRM供电芯片,都有一个vsense这样的一个pin,主要是用来采样输出电压,通过采样得到的电压,来调节输出电压的高低。所以这个采样点的位置比较重要。PowerDC可以仿真出这个采样点在哪里。感应线就是我们采样点放置的位置。

如果电源芯片只有一个负载,我们基本上可以把采样点放置于负载的输入点附近即可。但如果是多负载,这个采样点靠经验则不是很好估算,通过软件仿真比较方便。

有趣, 不错的功能!

多谢指教

我也想听大家的建议!谢

yinxiaowz.com

ademuz.com

小编能具体说说如何在PowerDC中设置这个sense line吗,还有VRM的sense pin如何设置呢,谢谢!

感应线:现在很多VRM电源模块会有一个sense管脚(很多工程师直接采样刚输出的位置,这是不对的),即采样管脚,举个例子:如3.3v电压输出后,到达芯片管脚是,会有一个压差,一般到不了3.3v,这时候,可以通过放置一个采样点,连接到sense pin(给单芯片供电,可以放芯片附近),这时候,VRM会调节输出电源,保证芯片供电稳定到3.3v。但是,如果负载芯片很多,采样点位置就不好设置了,要平衡每一个芯片供电都要稳定在3.3v,所以sigrity软件可以通过软件算法,给你算出一个可以放置采样点位置的区域,这个采样区域,我们称之为感应线。

不知道这样解释大家是否可以理解?

sense pin是必须你的VRM有这样的pin,然后软件里面有设置,打开即可。

谢谢小编的解答,明白了。

学习一下

:D:D

感觉好深奥

好牛逼啊

学习一下