用sigrity仿真ddr3的时序参数问题

时间:10-02

整理:3721RD

点击:

最近再看ddr3的时序仿真,对于参数的选择,也不知道自己理解的对不,我按照我的理解写出来,希望大家帮忙指错。

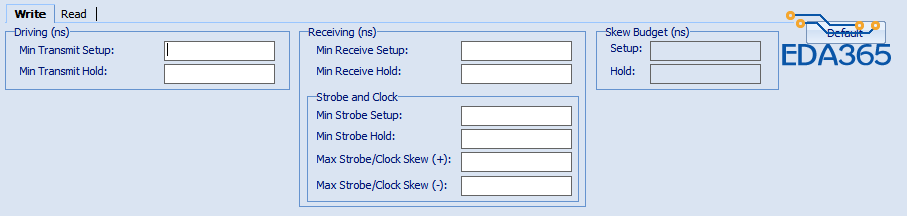

首先是wirte选项卡,这里用的ddr3,选用的control是freecale的某器件。

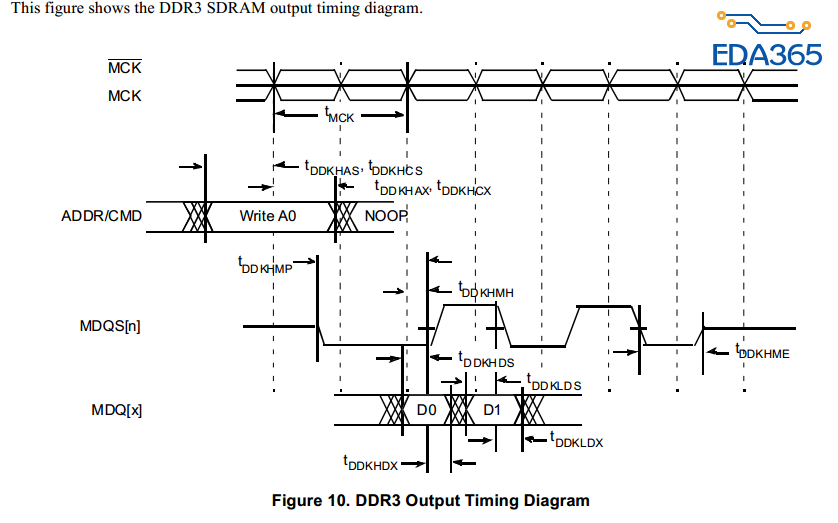

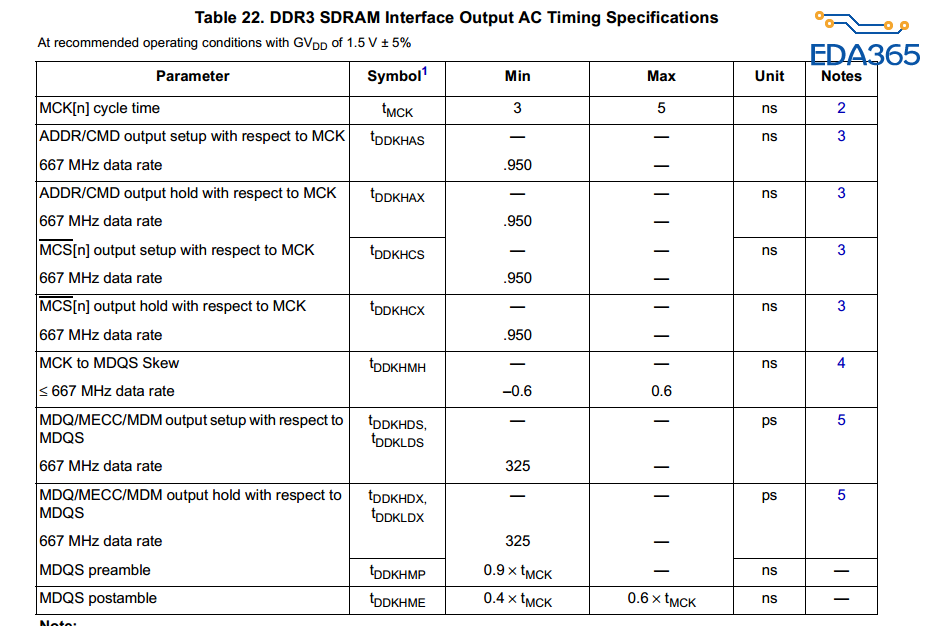

这里min transmit time指的就是tvb的值,也就dqs和dq(max)的差值,也就是图上的Tddkhds,然后tva应该是dqs和dq(min)的差值,也就是图上的tddkhdx,可是这个图上关于这两个值,都没有标注,请问怎么填写呢?

@shark845 求小编帮忙,

大神估计都在忙,我先继续吧,这是ddr3的时序图,

在Min Receive Setup,这时wirte选项卡,所以应该看dq inputing,也就是tds的值,关于电平的选取,其实无所谓,要保证和fly time选取一样的电平就可以,我猜想这个软件后面也有针对这个做设置,目前没做到那步,欢迎大家给出截图。这里我又有个疑问,这个base(specification)究竟是什么?这个vref@1v/ns 里面的值 应该是要根据 slew rating 做修正的吧。

Min receive Hold,也就是TDH

名字都写错了

你的理解是正确的!图上的两个值有标注最小325ps的