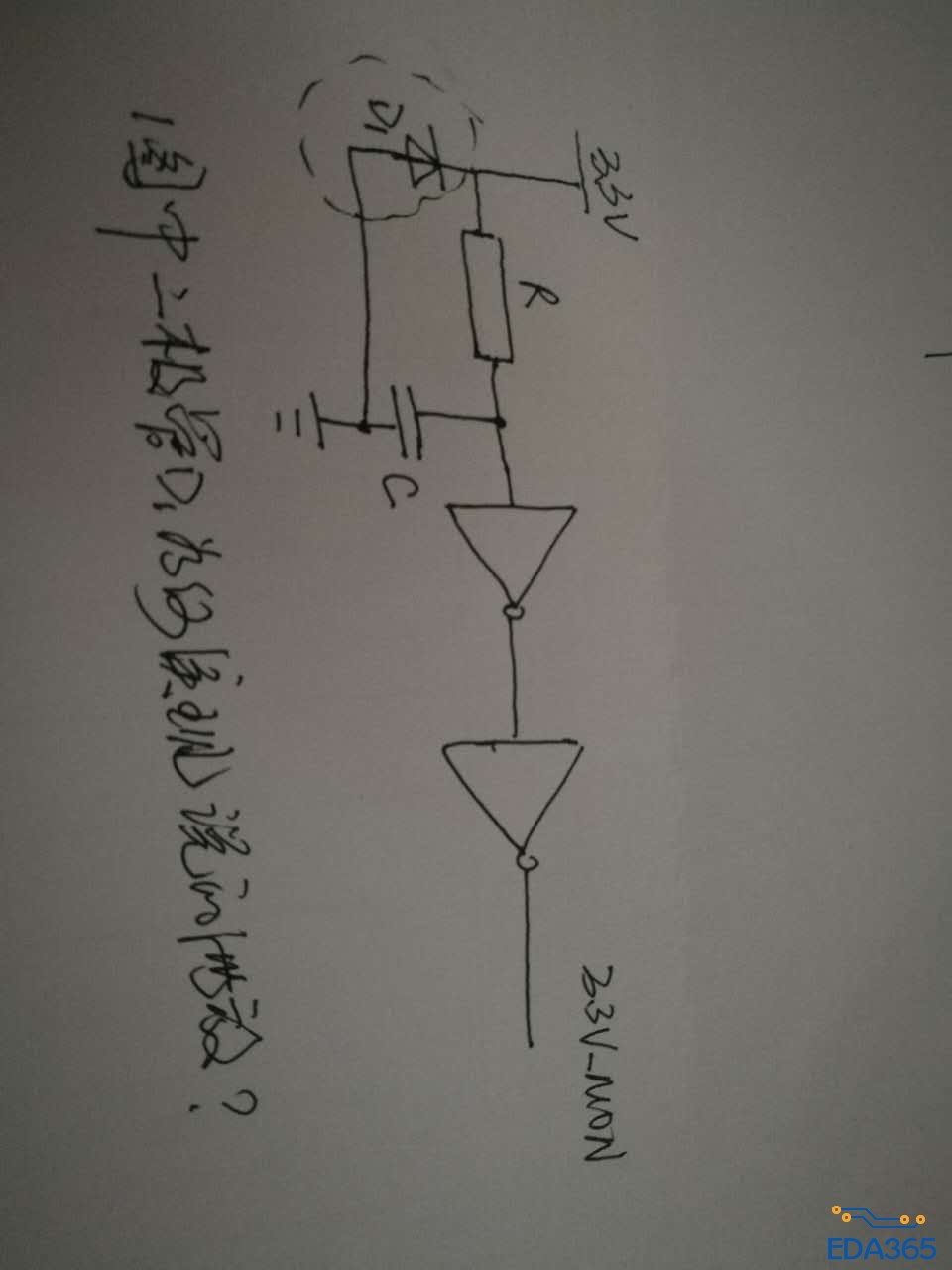

延时泻放电路分析

请大侠指教,谢谢!

一个电路的VCC和GND之间具有全电路等效元件,设是电阻,当有VCC电压时,这个全电路等效电阻对二极管和电容都不起作用;一旦VCC停止供电,由于电容上还有电荷,则这个全电路等效电阻便通过二极管(对于电容器上的电压来说该二极管正向导通,等效电阻很小,比RC电路的电阻小得多)加速将电容器上的电荷泄放掉,比通过RC电路的电阻放电快得多。

如果没有这个二极管的话,停电时电容器上的电荷只能通过元件的复位引脚放电,通过RC电路的电阻(阻值较大放电慢)放电,还有通过电容器本身的漏电阻放电,放电速度比较慢。

简而言之:掉电时图中R=56K,放电较慢 ,而肖特基二极管导通等效电阻2-3欧,放电较快。

錯了,應該是二極管正極接上面; 3.3V對地接二極管有毛有啊?

那3.3V不就直接通过二极管对地了。

二极管应该是和56K电阻并联,正极在电容端,负极在3.3V。不知道你看的资料出处是哪里,国内有些翻译资料甚至高校教材经常搞些莫名其妙的错误误导人

接二极管是为了你上电 ->断电 ->上电 。这种第二次上电情况下可靠的复位。

大神,没太懂你的意思,相当于电容接电源端多了一个对地的二极管,这个怎么放电啊?要是说这个二极管并联在电阻两端倒是有可能,前提是3.3V掉电之后存在对地的泄放路径。

接電容上面,就是並在電阻上。斷電時旁路電阻,加速放電;

您好!谢谢解释,但还是不懂。

二极管并非并在电容两侧,中间还是隔了那个放电电阻R呀。另外即便没有R,断电后,电容上面为正电压,下面为接地,二极管并在上面也是反向的,如何能够放电?

您好! 作用我明白,就是不知道按照我贴出的图纸整的话是如何给电容放电的。

您好。看起来确实应该是并在电阻上才对的。我是在一本“高速电路设计实践”的书上看到的。

前辈你好,不知断电时,电容是怎么进行回路的。

6楼说的是对的。二极管应该是和56K电阻并联,正极在电容端,负极在3.3V。

赞同6楼的观点,顶起