DDR2/DDR3设计中,阻抗控制的必要性问题

时间:10-02

整理:3721RD

点击:

今天看到如下一段话:

DDR走线线宽与阻抗控制密切相关,经常可以看到很多同行做阻抗控制。对于纯数字电路,完全有条件针对高速线做单端阻抗控制;但对于混合电路,包含高速数字电路与射频电路,射频电路比数字电路要重要的多,必须对射频信号做50欧姆阻抗控制,同时射频走线不可能太细,否则会引起较大的损耗,所以在混合电路中,本人往往舍弃数字电路的阻抗控制。到目前为止,本人设计的混合电路产品中,最高规格的DDR是DDR2-800,未作阻抗控制,工作一切正常。

有经验的同志说一下看法吧!

DDR走线线宽与阻抗控制密切相关,经常可以看到很多同行做阻抗控制。对于纯数字电路,完全有条件针对高速线做单端阻抗控制;但对于混合电路,包含高速数字电路与射频电路,射频电路比数字电路要重要的多,必须对射频信号做50欧姆阻抗控制,同时射频走线不可能太细,否则会引起较大的损耗,所以在混合电路中,本人往往舍弃数字电路的阻抗控制。到目前为止,本人设计的混合电路产品中,最高规格的DDR是DDR2-800,未作阻抗控制,工作一切正常。

有经验的同志说一下看法吧!

1 用共面波导方式做阻抗

2 如果是多层板,射频阻抗部门内层挖掉,再用共面波导方式做阻抗

3 射频加粗做阻抗与DDR做阻抗完全可以独立

是了,可以分开做。

另外,我还是想提一下,我的确是看到了那种DDR3不做阻抗控制的布线。

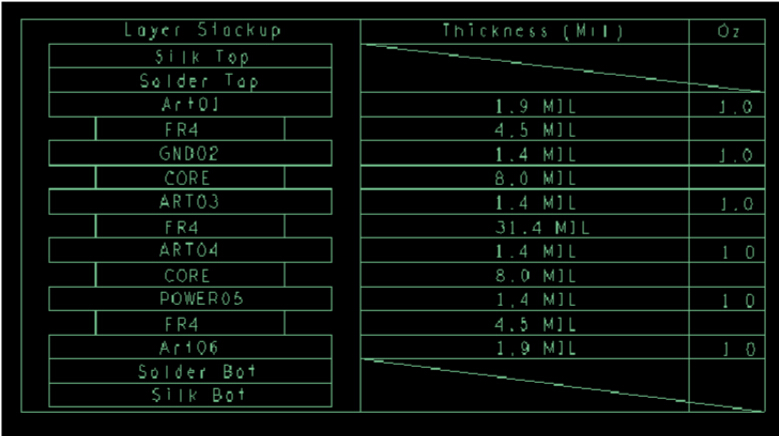

目标板层叠结构如图所示,DDR3布线在4个布线层都有布线,宽度都是4mil,power电源层在DDR3布线区分割出一块GND平面。但毕竟从TOP(Layer1)到GND(Layer2),和Layer3到GND(Layer2)的距离是不一样的啊?这样的话,从Layer1 的4mil走线,切换到Layer3时再走4mil的线,阻抗就不一样了啊?

[size=14.0000009536743px]可以调整叠层啊,ART01和ART03走线不需要一样粗,调整线宽,如果要做阻抗基本上是假8层去做了,不过还是比8层便宜。

这个叠层好控制阻抗的,如果需要,板厂可以帮你调整介质厚度和线宽

你自己计算下,就会发现很好做。

学习中

阻抗自己计算下,大概差不多就行了,没有绝对的,我是这么认为的。说到阻抗问题,有些硬件还真跟LAYOUT工程师扯蛋。

工作一切正常是在所有场景下都正常吗?有大批量长时间运行无故障的实际验证吗?可靠性是设计出来的,不是靠蒙。