Open Drain 硬件结构肤浅的研究

时间:10-02

整理:3721RD

点击:

“鹏哥,I2C接口为什么总是要外接个上拉电阻?”

“它是Open Drain结构。”

“哦!牛逼!”

我操,谁能告诉我 Open Drain到底是什么鬼?

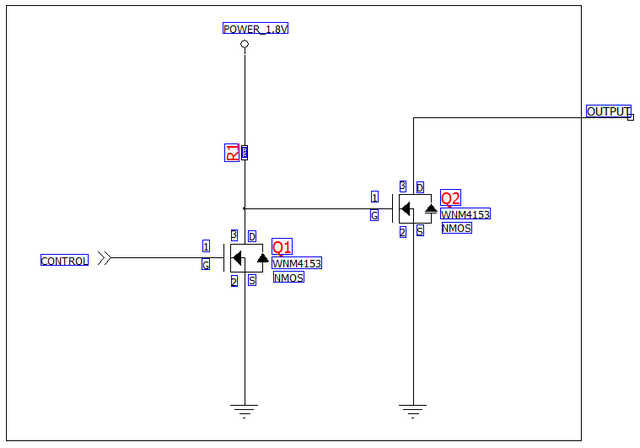

Open Drain,翻译过来就是开漏,意思是把MOS管的漏极不连接,悬空。手绘一个:

开漏,是把上图电路中的Q2的漏极悬空。Q1是用来控制Q2的开关的。

当CONTROL=Low 时,Q1断开,Q2导通,OUTPUT= 0;

当CONTROL=High时,Q1导通,Q2断开,OUTPUT处于悬空状态。

所以Open Drain的第一个特点:此结构本身只可以输出低电平(Low)。

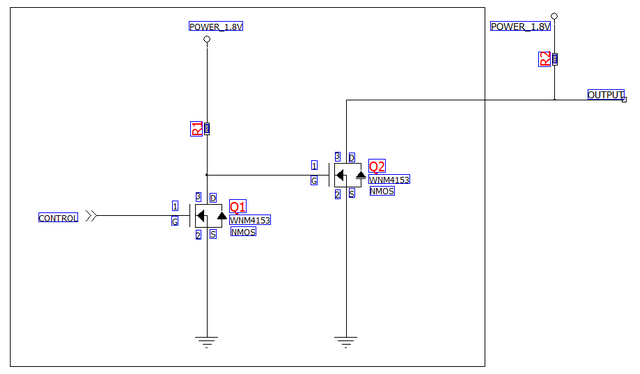

如果在OUTPUT端通过一颗电阻R2连接到POWER_1.8V,这种结构就有了输出高电平的能力:

当CONTROL=Low 时,Q1断开,Q2导通,OUTPUT= 0;

当CONTROL=High时,Q1导通,Q2断开,OUTPUT=1。

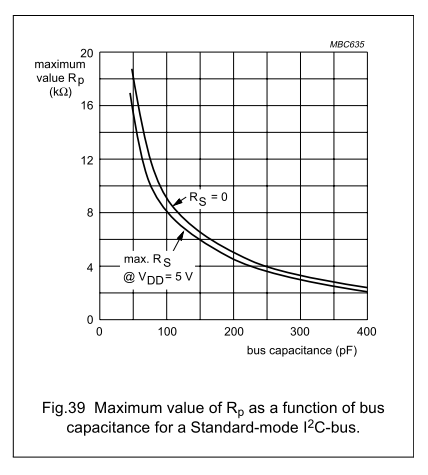

R2的就是常说的上拉电阻,它的取值不是随便的,需要根据OUTPUT上的等效容值来选。在I2C的SPEC中第40页,专门画出了R2和等效容值的关系:

图中可以看出R2(纵坐标Rp)和等效容值成反比例关系,简单地根据OUTPUT的波形来说:

R2越大,OUTPUT上的上升沿越平缓;R2越小,OUTPUT上的上升沿越陡峭。上升沿的平缓程度就是我们常说的上拉能力。越陡峭,上拉能力就越好。

需要注意的是,R2越小,功耗就越大。所以,R2要根据实际情况调整:先放一个大的上拉电阻,然后测量OUTPUT的波形,如果上升沿很陡峭,可以

考虑再放大点;如果上升沿太平缓,那应该放小点了。

MTK老的平台,I2C的上拉电阻放的是2.2K。新的平台都用4.7K上拉,这也说明了MTK的CPU制作工艺在提高。

同样,这是 Open Drain 第二个特点:如果要输出高电平,需要外接上拉电阻。

将两个 Open Drain 连在一起,只要有一方输出Low,这条OUTPUT就只能是Low了。I2C协议中,如果设备要占用总线,需要输出Low电平,就是这个原理。

这是 Open Drain 第三个特点:逻辑与,多个Open Drain的漏极接在一起,就相当于“逻辑与”的功能。

Open Drain 除了用在I2C上,它还有一个重要的应用:电平转换(Level Shift)。

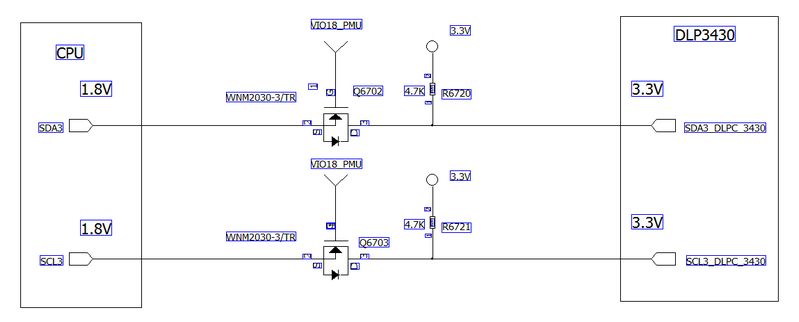

在N355上用 Open Drain 结构搭建了一个I2C上3.3V与1.8V的电平转换,如下图:

这个电路很有意思,1个IO电是1.8V的CPU与IO电是3.3V的IC本身是不能接在一起的,但通过这个电路,它们不仅接在一起,还可以进行I2C通信!

当理解了这个电路如何进行I2C通信之后,也就理解了电平转换。这个电路在进行I2C通信的时候,有下面四种情况:

CPU发High电平(1.8V),Q6702/Q6703的Vgs=0(Vg=Vs=1.8V),两个MOS关断,IC端还是High电平;

CPU发Low 电平(0V),Q6702/Q6703的Vgs=1.8V,两个MOS打开,IC端的高电平被拉低;

IC端发High电平(3.3V),Q6702/Q6703的Vgs=0(Vg=Vs=1.8V),两个MOS关断,CPU还是High电平;

IC端发Low 电平(0V),Vs=1.8V,Vd=0V,MOS管内的二极管导通(MOS管结构所致,S极和D极之间有个PN节,相当于二极管),CPU的高电平被拉低。

欢迎指出错误

哇!好详细的开漏研究,小编辛苦了!

不错

有错误的话请指正哦

找PCB工程师合作,可以在此处留言

找PCB工程师合作,可以在此处留言

好东西

总结的还可以,总线的上升沿时间是R*C常数决定,驱动能力看集成管的参数,外部电阻只是提升驱动能力,理解有误请拍砖!

Heng,上升沿的时间也是一种驱动能力的体现

那个电平转换电路的左边(CPU这边)通常也要加上拉电阻,拉到1.8V,而且P-MOS的S-D之间并一个二极管(稳定可靠)

那个电平转换电路的左边(CPU这边)通常也要加上拉电阻,拉到1.8V

——这都被你发现了,是我漏了,其实这个电路还有前端部分,在CPU那端已经上拉了。

而且P-MOS的S-D之间并一个二极管

——用的是N-MOS

学习下~~~~~~~~~~