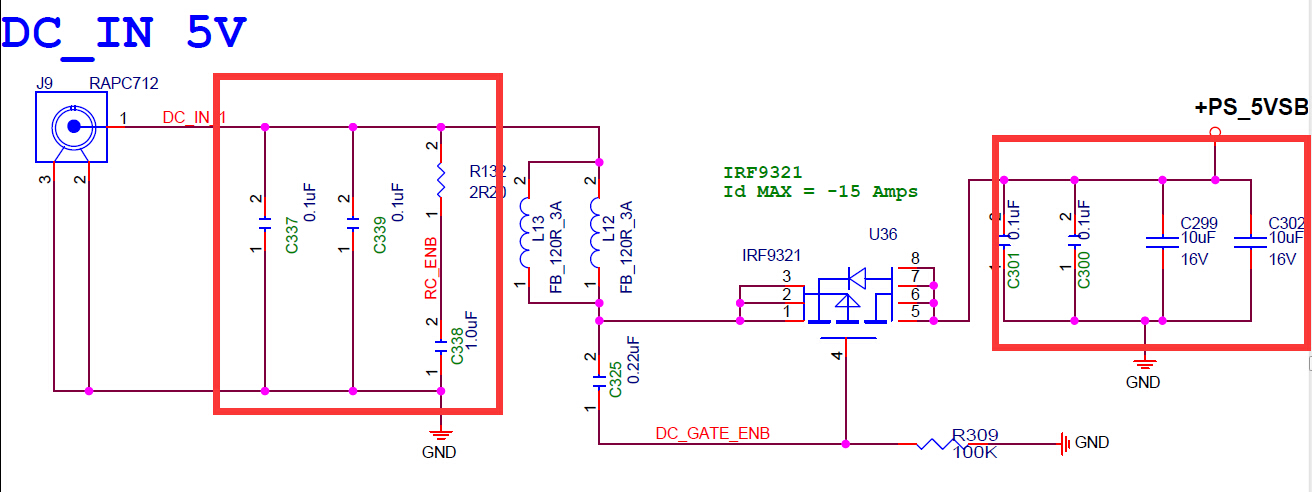

关于电源输入处的滤波电容安排的疑问?

一直有个疑问,今天鼓起勇气问出来。就是这个电路的滤波电容为什么要用这个数量和容值,其中的道理是什么?

如果我来设计这个电路,基本上是:左边框放一个104;右边框也放一个104,哪天心情好(?),最多加个10u的电容。根本不会做成这样。

我当然知道如图示处理会得到一个更干净的电源,问题是有必要么?在入口做这么精细的设计有必要么?不是只要在具体电路/芯片处做好去耦就可以了么?

哇 很好的滤波电路

怎么好了?好哪里呢?可以说说你的理解么?

EMC实验时 ,电源是一个不可忽视的干扰源,处理好才是重点

小电容去高频干扰,大电容串联小电阻目的是降低整个电容的Q值,防止上电瞬间和电感合作感生出较大震荡电压,PMOS主要是缓启,后面的电容大小主要看你负载的需求,比如抽取电流的斜率和允许的瞬态压降

先谢谢你的回答。对于这个电路的各部分的作用,大概是清楚的。我真真的问题在电容数量的安排和容值的选择上,在计算上。

挂载电容的大小和数量都是和后端的负载有直接关系的,你得负载特性都没说,估计只能小编能帮你掐指算算了

我也想知道1.0uF跟2.2Ω的电阻串联这个值怎么配的?经验值?

按我说,这种配置并非就是合理的。

两个相同容值的电容并联,不如不同容值并联得到的阻搞更小,去耦频率范围更宽。

电容的作用就是给电源和地回路之间提供一个低阻抗路径,阻抗越小越好。

C=Q/U=delta It/delta U, 当delta I 很大时,要想delta U很小,就必须C很大,这是时域上的理论依据。

频域上看,电流的波动必然引起某些频谱上出现信号,想不让这些信号传导出去,就得想办法把这些频率信号短路到地,选一种谐振频率正好落在这种频率上的电容,使之对地呈现低阻抗。大电容谐振在较低的频率,小电容谐振在较高的频率。对电容来说,ESL,ESR越小越好。

这么做是有一定好处,但是不同的容值,这个容值之间的数量级差异可得把握好,不然的话在某些频点处出现较大的反谐振则会放大杂讯影响;多放0.1uF显然是经验做法,它的谐振频率对于电源上较为关心的相当一部分杂波有很的滤波作用,能有效降低电源阻抗,不过随着IC工艺的不断提升,信号上升时间的不断缩短,合理地“打组合拳”还是很重要的

学习了。

学习了

这个是电源的入口,要说负载的话,就是后面整个电路系统,那太复杂了,根本说不清啊。

这么说来,基本上还是经验做法咯?

实际上,到底安排几个电容,容值多大,这个的确不好算。

另外,我们是不是只要在各自的模块电路或芯片处做好去耦就可以了,而电源的入口处是否有必要像这个电路这样放好几个电容做系统级去耦呢?