帮忙分析一下这个P-MOS控制线路

时间:10-02

整理:3721RD

点击:

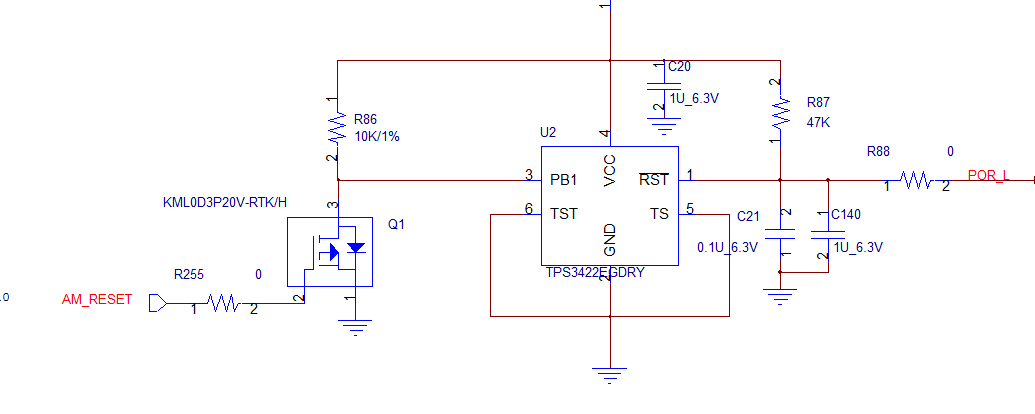

AM—RESET 为GPIO控制, 现在这一Pin 悬空。

问题:

上电后,在AM—RESET 悬空的状态下 Q1 的1,3 Pin即 DS导通,D极对地了。

设计的打算是GPIO给低电平的时候MOS才导通。

我的理解是此状态下DS截止才对,对与MOS管经常困惑,请大家帮忙看一下这个线路如何改? G端加一个上拉吗?

你这杨还不如用三极管。

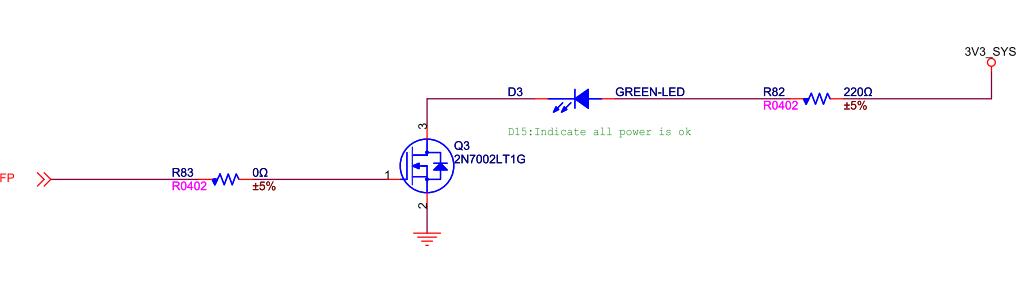

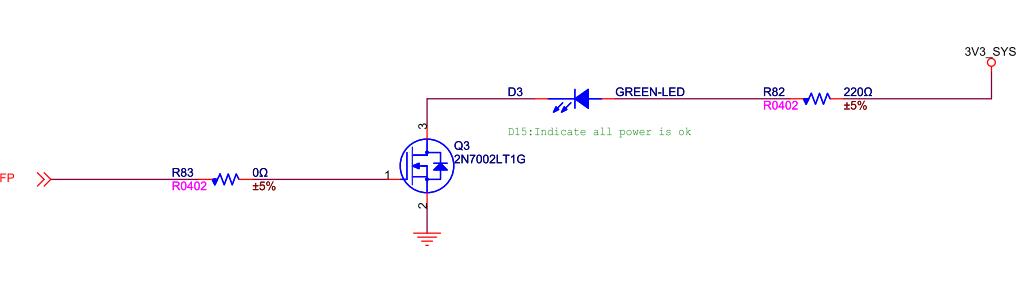

看下面这个图。能看懂把?

问题:

上电后,在AM—RESET 悬空的状态下 Q1 的1,3 Pin即 DS导通,D极对地了。

设计的打算是GPIO给低电平的时候MOS才导通。

我的理解是此状态下DS截止才对,对与MOS管经常困惑,请大家帮忙看一下这个线路如何改? G端加一个上拉吗?

MOS管反了。你这样不就相当于是直接用MOS管中的二极管到地了么,你仔细看看图,想一想就出来了。1,3对调

1,3对调

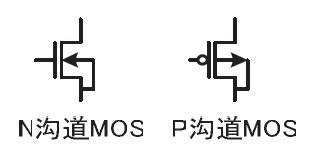

要是没看错的画,你用得是PMOS?

你这杨还不如用三极管。

看下面这个图。能看懂把?

体二极管存在导通 你这样用不行的 做开关pmos 为S-》D s接电源 mos管忌讳栅极悬空 Pmos最好上拉 低电平导通

MOS管反了

MOS管子画反了,而且MOS管最好不要悬空

记住一点,一般这种利用MOS管进行逻辑转换的都是OD、OC输出,所以你的管子是反的。

控制到地的 最好用N MOS 不然 GS 怎么控制

楼上说的都好有道理。