关于SD卡的一个奇怪问题

时间:10-02

整理:3721RD

点击:

一个新项目中使用的SD卡出现数据写入出错的问题,出现的概率很低,写入几百M数据大概会出现一次。

SD 时钟为50M,单边采样,对比之前图纸发现SD卡CLK线上增加了一个10pF电容,EMC工程师为了防止EMI超标,建议增加的,所以怀疑CLK信号有问题,测量发现CLK信号除了上升沿较缓外,无其他问题,上升时间大概为5ns,但是建立、保持时间完全满足SD卡协议要求。

然后怀疑会不会是时钟抖动较大,导致某些数据建立保持时间不满足,而在单次波形测量中没有抓到,所以进行时钟抖动测试,测试发现时钟DJ抖动较大,为2ns,到此以为找到了问题原因,但是不放心,还是再确认一把,将CLK频率将为25M,这样就算有抖动,就算时间上升时间较大,建立保持时间也是够够的,但是测试发现写入数据还是会出错。

到此,彻底没有了方向,翻看SD卡协议,发现高速卡对时钟上升时间有要求,要求不能大于3ns,难道是这个原因导致数据写入出错?将10pF电容删除,测试发现CLK上升时间提升至2.8ns,输入写入发现没有再出现之前的错误,测试n遍,写入了几个GB的数据还是没有出现错误。

问题来了,难道真的是上升时间不满足导致SD卡数据写入出错?实在是不能理解,建立、保持时间完全满足,单单这个上升时间不满足会导致数据出错?实在不能相信最后的结论,一直认为很多总线中对上升时间做规定,只是为了要满足建立、保持时间,难道CMOS电路内部锁存器神马的对这个时钟上升时间有什么特殊要求?

恳请大神帮忙解答一下小弟的困惑,万分感谢。@超级狗

SD 时钟为50M,单边采样,对比之前图纸发现SD卡CLK线上增加了一个10pF电容,EMC工程师为了防止EMI超标,建议增加的,所以怀疑CLK信号有问题,测量发现CLK信号除了上升沿较缓外,无其他问题,上升时间大概为5ns,但是建立、保持时间完全满足SD卡协议要求。

然后怀疑会不会是时钟抖动较大,导致某些数据建立保持时间不满足,而在单次波形测量中没有抓到,所以进行时钟抖动测试,测试发现时钟DJ抖动较大,为2ns,到此以为找到了问题原因,但是不放心,还是再确认一把,将CLK频率将为25M,这样就算有抖动,就算时间上升时间较大,建立保持时间也是够够的,但是测试发现写入数据还是会出错。

到此,彻底没有了方向,翻看SD卡协议,发现高速卡对时钟上升时间有要求,要求不能大于3ns,难道是这个原因导致数据写入出错?将10pF电容删除,测试发现CLK上升时间提升至2.8ns,输入写入发现没有再出现之前的错误,测试n遍,写入了几个GB的数据还是没有出现错误。

问题来了,难道真的是上升时间不满足导致SD卡数据写入出错?实在是不能理解,建立、保持时间完全满足,单单这个上升时间不满足会导致数据出错?实在不能相信最后的结论,一直认为很多总线中对上升时间做规定,只是为了要满足建立、保持时间,难道CMOS电路内部锁存器神马的对这个时钟上升时间有什么特殊要求?

恳请大神帮忙解答一下小弟的困惑,万分感谢。@超级狗

狗然素一位用功的工程師,很常見的問題、但很少人會去深究原因。

前座的工程師幾個禮拜前剛好也遇到這問題,後來是改主控端 SD 總線的驅動能力(Driving Strength )解決。

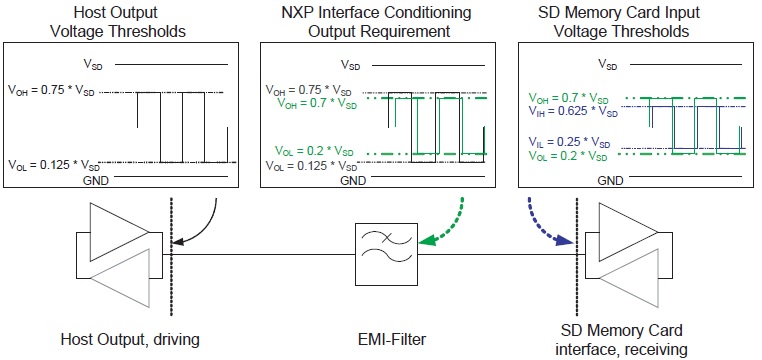

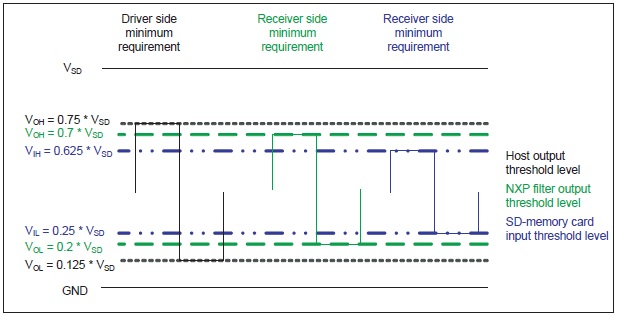

這個問題的說法有很多,各有其支持的擁護者。講時鐘的上升時間(Rising Time)及下降時間(Falling Time)造成的也不算錯,嗯插屁(NXP)的技術文檔,或許可以給我們一些啟發。

狗小编的意思是SD卡端信号幅值不满足SD卡的最小输入阈值要求?

也遇到这个问题过,但不是说读不了数据,而是上升时间超标,后来也是通过修改驱动能力解决的

以前也见这样的问题,后来排查发现SD 的数据线和CLK 的ESD (体电容太大)贴错啦。

没见过这样的问题,收藏一下。

小编问题解决了请反馈一下解决办法哟

写入错误 我也遇到过 CLK 并接电容 不能放 还有走线距离长度 也有影响

最后想问问 @超级狗 SD卡走线 到底要不要走等长之类的

mark

和CLK的时序确实有很大的关系