电脑主板中为什么两个三极管这样用?会导通吗?

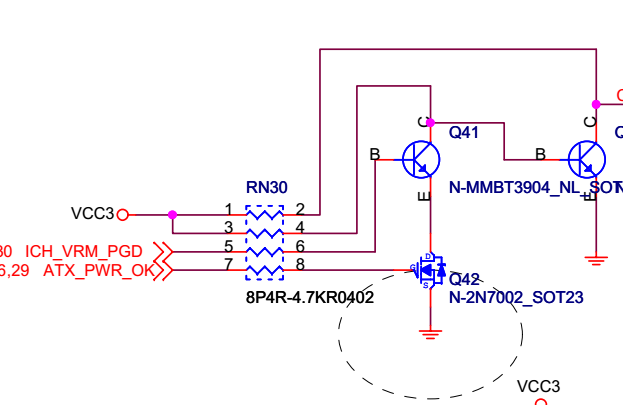

以下两张电路图,是在某品牌电脑主板中所用的控制电路,想不明白为什么会如下面两图这样用?

都是NPN上下串联在一起,那样能导通吗?上管的开启电压需要多高?

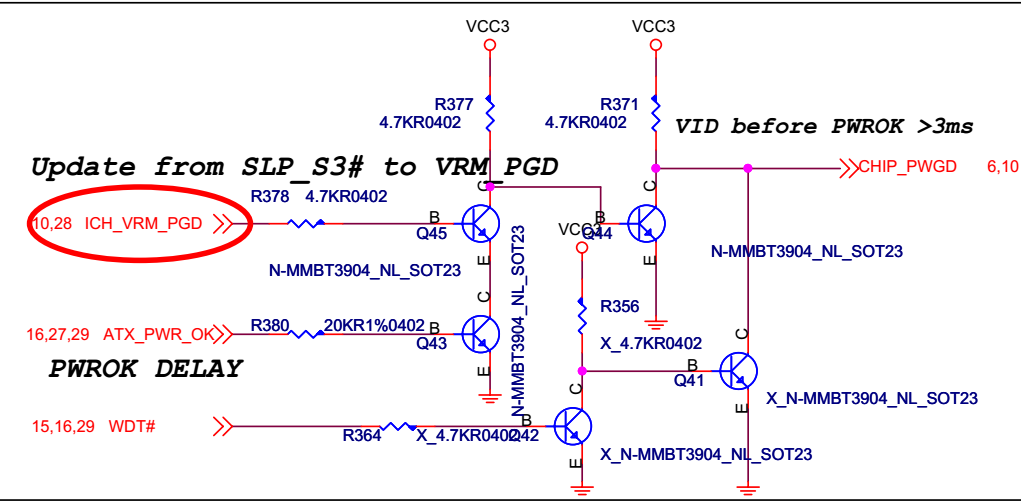

当Q43和Q45的B极都是高电平输入的时候(1.8/2.8/3.3),Q43的C极肯定是有一个电压的,那么这个电压V有两种可能,要么高于Q43的B极,Q43为放大状态,要么V低于Q43的B极电压,那么管子会工作在饱和状态,通过计算可以知道,最终管子都会工作在饱和状态,那么VCEsat就会很小,应该不会高于0.6V,如果深度饱和的话可能更低0.3,那么你Q45的B极电压只要高于1.4V即可导通。

可以的,我们就这样用过,不过用的是两个NMOS串联的,形成一个与门输出,作为下级电源使能,这个与cascode电路很像。

我理解Q45,Q43的作用是与非门逻辑,PG和power OK信号都为高电平时,两个串联的管子都导通,进而Q44的三极管B极拉低,open drain 输出高电平。Q42相当于反向器,把输入信号取反,再通过Q41与Q44并联形成与门。以上这样的逻辑,我们在控制系统电源上电时序上用过,不过是NMOS,输入信号电平1.8V就可以。

你纠结的应该就是两个三极管相连处的电压,我看到上管的C极有一个4.7K的电阻,而电源电压只有3.3V,最大的负载电流也只有3.3V/4.7K=0.7ma,也就是说只要很小的Ibe就会让管子就饱和(假设管子直流放大系数为100),同样下管也将会工作在饱和状态,那么VCEsat=0.3V,两管相连的地方的电压基本和接地没多大差别,所以你上管的B集电压也不用多大就能让上管导通。

以上只是个人粗浅的理解,如有不对的地方还请不吝指教。

大神,还没出来,不能让帖沉了

得 SPICE 模擬一下就出來了

不用想那么复, 就一相与的关系。两个三极管同事导通输出才是地电平,只要一个不导通输出就是高电平,和那个三极管先导通后导通没有关系