请教一个关于I2C被拉低的问题

时间:10-02

整理:3721RD

点击:

主芯片使用的是RK3188 上拉电阻是10K。

挂在L3G TSC2007 ADS7923 3款芯片。

L3G和ADS7923都正常工作。

但是每次我一读TSC2007。I2C的SCK时钟脚就被拉低。

求教这个是什么问题?

我把上拉电阻改成1.5K,不会出现拉低了。

但是,

2007死活认不到。

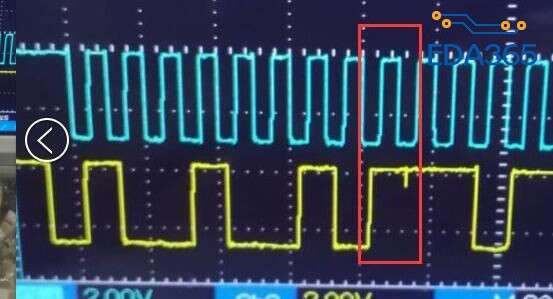

抓出来的波形是这样的

挂在L3G TSC2007 ADS7923 3款芯片。

L3G和ADS7923都正常工作。

但是每次我一读TSC2007。I2C的SCK时钟脚就被拉低。

求教这个是什么问题?

不知道我理解的对么,你在读TSC2007之后,clk信号就不能跳变了,一直是0对吧。SDA发送W/R之后slave有没有ALK

或者你把电路图跟layout发一下。

你的clk被拉低了那你的data不是随时都可以变化?

我把上拉电阻改成1.5K,不会出现拉低了。

但是,

2007死活认不到。

抓出来的波形是这样的

额,好巧啊,刚在pads群里也是你问的吧,回答得也是我.换成1.5K,上拉的驱动能力应该更强了,为什么你这个拉低的问题解决了,不明白.

slave 器件有问题吧,看你刚说的clk持续拉低,有种可能是总线问题导致,被锁存了。

这是怎么锁存的?

正在学习研究RK3288

没有及时回复ACK吧,从设备拉低的

http://blog.csdn.net/zyboy2000/article/details/5603091

学习

觉得还是从设备的问题,主机送的地址都正常,从设备发回No_ACK,,查一下上电时序吧,

看到波形是SLAVE没有回ACK信号,回的是NO_ACK。请问解决了么?