PCIe接口失效问题分析实例

引 言

PCIe是一个在很多领域中都有着广泛且重要应用的接口,经过十几年的发展,PCIe接口已经从1.0发展到现在的3.0,4.0也已即将开始应用。PCIe技术的物理层基于串行SerDes技术,因此用极少的物理连线就可以实现高速的数据传输。笔者在前段时间碰上了两个PCIe接口失效的问题,第一个经过分析是PCIe的ESD防护没有做好导致通讯中断,第二个是电源负载过大导致PCIe供电异常,FPGA PCIe IPCORE逻辑时钟失锁。现把这两个问题的定位和解决过程与读者一同分享。

1. 系统概述及问题描述

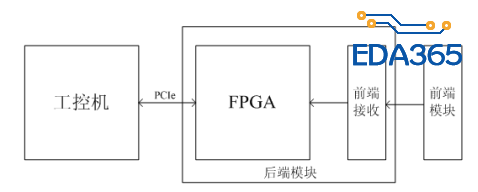

现简略的介绍该系统,其简略框图如下:

图1

该系统由两个模块组成,前端模块可插拔,在插入后会传输信号给FPGA,信号经过前端接收,A/D采样后进入FPGA做信号处理,然后FPGA把处理过的信号通过PCIe接口传送给工控机进行后处理及显示。工控机也会通过PCIe接口控制FPGA的工作状态。前端的模块是可插拔的。

第一个问题是该机器在做测试时,发现在换模块时会偶发的出现工控机与FPGA的通讯异常的现象,该现象出现的频率很低,测试组的同事反馈在做测试时经常会有换模块的操作,但该现象基本上几天才出现一次,虽然该现象概率低,但是问题影响甚为重大,必须攻破。

第二个问题则是系统不接交流电而使用电池运行在某种模式下,在达到10%低电量时,会必发的出现PCIe通讯异常。

2. 第一个问题定位及解决过程

该问题的定位开始是没有头绪的,因为问题出现后,PCIe的通讯已经中断,此时想通过工控机去读FPGA的调试相关的寄存器已经没有用,即此时读上来的值都是无效的。但是还是得先逐步的排除问题。

第一步:是否是软件的问题:

通过阅读问题发生时的软件日志,发现在问题发生时,软件没有收到中断请求,这说明在插拔模块的过程中,PCIe通讯已经失效,模块插入/拔出的中断已经无法发出(在模块插入或者拔出的过程FPGA会检测,如果发生该事件FPGA会通过PCIe发出中断给工控机)。且在问题发生时软件日志的记录上软件没有异常之处,因此排除是软件的问题。

第二步:是否是FPGA逻辑的问题:

通过在FPGA插入在线逻辑分析仪,把PCIe的运转状态机LTSSM加入到在线逻辑分析仪,在发生此问题时触发观测LTSSM状态机。在测试时,复现该问题后发现LTSSM有重新回到复位状态的动作,因此怀疑此时可能是电源或者是PCIe接口复位信号的问题,因为在正常情况下,如果系统复位信号没有动作,且上位机没有重新发送PCIe链路训练命令的话,LTSSM状态机是不会被复位的。因此该线索把该问题的原因导向到复位信号或电源上。

第三步:监测PCIe接口的复位信号

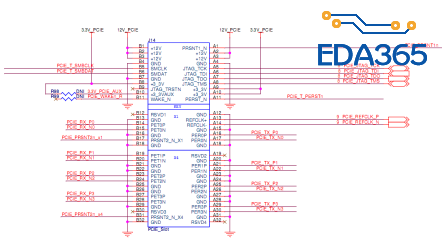

PCIe接口的电路如下图所示:

图2

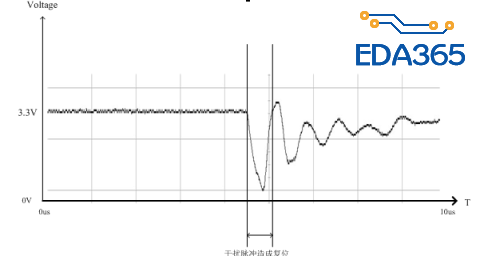

由上图可以看到,PCIe接口由数据接收差分管脚PCIE_RX_P,PCIE_RX_N,数据发送差分管脚PCIE_TX_P,PCIE_TX_N,以及SMBUS(SMBCLK, SMBDAT),JTAG管脚,参考时钟PCIE_REFCLK_P,PCIE_REFCLK_N以及复位管脚PCIE_PERST_N组成。其中JTAG管脚和SMBUS可以不连,参考时钟也可以选择用本地时钟或者选用接插件过来的PCIE_REFCLK_P,PCIE_REFCLK_N。前面提到,由于重点怀疑复位信号有所动作,因此对该复位信号用示波器进行监测。在若干次实验以后,发现在某次插入模块后失效时,捕捉到了PCIE复位信号PCIE_PERST_N有一个持续时间约为2.3个us的低电平脉冲,正是该脉冲信号让FPGA的PCIE IPCORE复位,导致PCIE通讯中断的原因。该脉冲信号如下图所示:

图3

该干扰脉冲从何处而来?经过实验发现是静电导入。我们在插拔模块时,由于模块本身外壳有部分金属,因此静电从外壳金属进来后经过某些路径耦合到PCIe复位线上,引发了该问题。

问题解决思路:找到问题来源点,解决方法就多种多样了。在此笔者推荐三种方法一起用:1. 对PCIE_PERST_N复位信号加滤波;2. 做好整机/模块的ESD保护;3. FPGA对PCIE_PERST_N信号做判断后再引入FPGA的PCIe IPCORE复位端,即对PCIE_PERST_N信号做低脉冲时间计数,大于规定的ms级低电平才判断为复位,否则则判断为干扰信号,FPGA控制逻辑不去复位PCIE IPCORE。

3. 第二个问题定位及解决过程

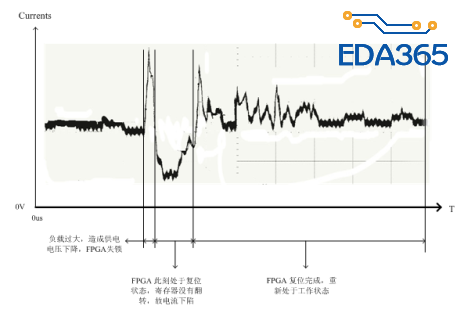

该问题的定位比第一个问题定位简单。因为该问题是在带电池低电量时必发,在插上交流电时则没有该现象,因此可以排除软件和FPGA逻辑问题,因此把问题聚焦在电源上。通过示波器实地测试,发现在电池低电量且工作于该模式下,电流有突然增大的现象,导致此时电压跌落,引发FPGA逻辑时钟失锁,由于FPGA逻辑的设计是使用逻辑系统时钟锁定信号作为PCIe IPCORE部分逻辑的复位信号,因此此时会导致FPGA的PCIe IPCORE被复位,进而产生PCIe通讯失效的现象。现在来分析一下整个过程,该时刻波形记录如下图所示:

图4

如上图所示,黄色的波形为系统电流波形,使用电流探头测量,绿色和青色波形为模块某部分调压波形,非FPGA PCIe供电电压,在此处可以认为跟笔者的分析无关。比较遗憾的是,这个截图中没有记录下FPGA的供电电压,有记录的图笔者没有找到。但是该图可以很明确的分析此时系统电流变化的过程:在某种工作模式下,电流突然急剧上升,此时会造成FPGA供电电压发生变化,进而导致FPGA逻辑时钟失锁,进而造成FPGA逻辑复位,由于此时FPGA逻辑处于复位状态,寄存器不再翻转,因而系统供电电流突然急剧下降,此时可以对应到上图的电流急剧下跌,由于电流下跌,负载减轻导致FPGA工作电压回复正常,时钟重新锁定,FPGA逻辑复位完成,重新工作,因此电流又重新回复到比之前模式切换时的功耗略少的状态。整个过程是一个链式反应,非常清晰的被记录在示波器上。

问题解决思路:改善电源模块供电设计,增加裕量。

4. 总结

对于PCIe接口的稳定性设计来说,电源和时钟是关键,在保证了电源和时钟的稳定性以后,还需要注意对关键敏感信号的保护,在有外部接插,触碰动作介入系统的情况下,注意对PCIe接口的敏感信号,如复位信号的保护是非常有必要的。

确实是这样,很多工程师都会在clock上遇到问题

谢谢分享!

给力

ESD的这种问题源头太难找

我也出现过这种故障。不过当时FPGA工程师不熟PCI,最后都是用示波器直接量PCI上电波形的,发现也是有干扰,加个电容滤波后彻底解决了。

谢谢分享!谢谢分享!

ESD的这种问题源头太难找

学习学习

这个确实很难控制,

谢谢分享