这个电路是怎么实现的?它的原理是什么?

时间:10-02

整理:3721RD

点击:

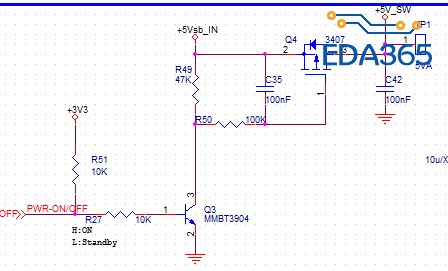

这个电路是怎么实现的?它的原理是什么?详情的帮忙解说下。谢谢!

通过PWR-ON/OFF控制Q3的导通状态,当满足Q3积极导通、管子处于饱和状态后相当于Q4的栅极通过R50和Q3下拉到地,Q4导通,完成+5v给+5v_SW的供电.其中C35缓冲电压上电过程,R49限流。

Q3是个开关型的三极管,Q3的基极电流控制着Q3的导通与关断,

当Q3关断时,Q4门极为高,Vgs>0 Q4关断,

当Q3导通时,Q4门极被拉低到地,Vgs<Vth (Vgs=0),故Q4导通,电源从5Vsb_in流向5V_SW.

这里需要选择Ron导通电阻小的PMOS,尽量减少压降的影响。

这个是一个P-MOS,不是N-MOS,这么说的话,你应该很容易就明白了吧?

IO口控制MOS管通断。默认是H,MOS管常开。

缓上电。

建议回去看模电

R27电阻应该减小一点,也可以删掉。PWR_ON/OFF为高,Q3导通,Q4.1为低电平,Q4导通。+5V_SW输出电压等于+5Vsb_IN。

PWR_ON/OFF为低,Q3不导通,Q4.1pin为高电平,Q4也不能导通。+5V_SW输出电压为0V。 这就是一个带有使能控制的电源开关电路。解释完毕,如有雷同,肯定见鬼!

典型的MOS开关电路,IO口控制MOS管通断

100K会不会大了点

不大 ,只是减缓mos开启速度而已

Mos 开关速度可以上兆的

注意IO是OC还是OD类型,是否要上拉电阻

软控5V开关电路

学习顺便赚个分

缓上电是靠R35 跟C50吗?