RGMII 收发信号各有一根enable 信号, 是否需要与clock 等长

RGMII 有收发信号各一组

RxCLK, RXd0, RXD1,RXD2,RXD3, RXen

Txclk, Txd0, Txd1, Txd2, Txd3, TxDv

我的问题是

收或发中的en / dv 信号, 在pcb 走线设计上, 是否需要与各自的clk 等长?

有人说不需要。enable只是一个简单的开关。

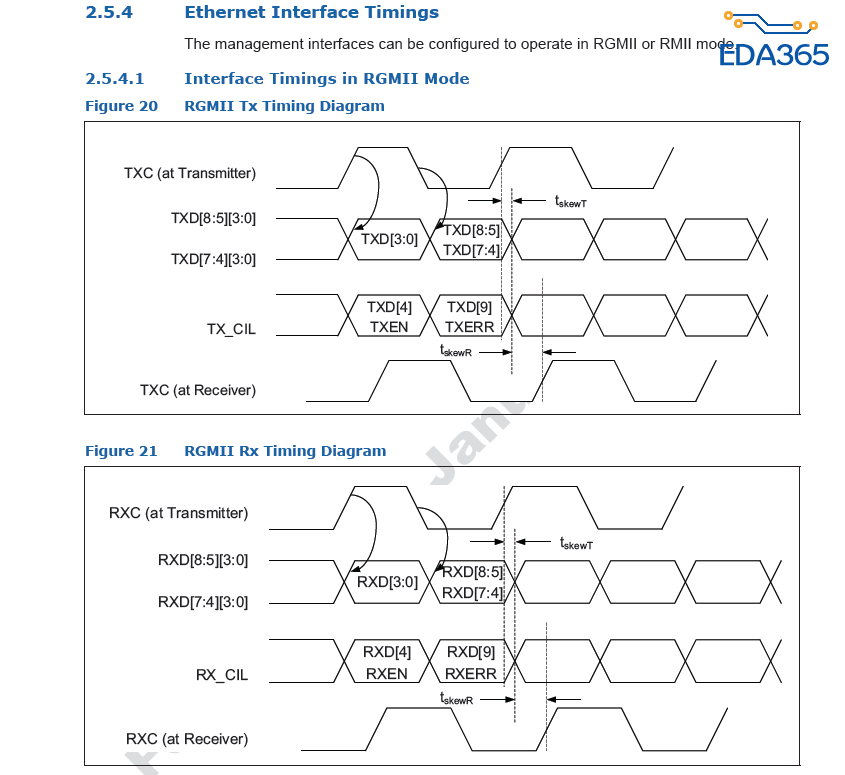

也有人说需要, 理由就是附件的那个timing diagram。

diagram中说的setup 与 hold 是否就是指锁存?--似乎不太对。

谢谢!

timing

diagram

需要啊,图上很明显看得出来,TRX_CIL和DATA一样,在上升下降沿有不同含义,EN ERROR,图中的时序的skew很明显不仅指DATA,还包括CIL信号,假设你收到的数据出现连续错误,ERROR信号就有作用了,如果时序不对,很显然就可能出问题。

但是RGMII这速率,一般来说,不容易出问题,基本这一把线拉出来误差不会太大,超过上千mil再考虑下等长吧,表示从来不做等长,时序刚刚的。当然不做时序补偿(不升等长)的话就要用delay来保证RGMII模式下的DDR时序要求了

谢谢!Kevin

估计是我理解错了。

1. TRX_CIL 与 其它的enable 功能不太一样。 很多时候Enable 的功能,和power-good 相似。

2. 功能上, 很难理解, enable为何要与clk有时序对应关系。从图上看, 似乎CIL 与data 是同步的跳动。 可是, 传输逻辑是什么呢?TXD(4-9)指的是什么呢?

3. 速率上,T-scew is 0.5 ns, T-setup and T-hold are both 1 ns. 按照5600mil/ns stripline. 它们的tolerence就是2800mil. 可是, 芯片供应商及我司的SI 专员给出的要求却是+/-25mill 的等长tolerence。 这算是严格吗?还是浪费时间,精力?

谢谢!

学习了

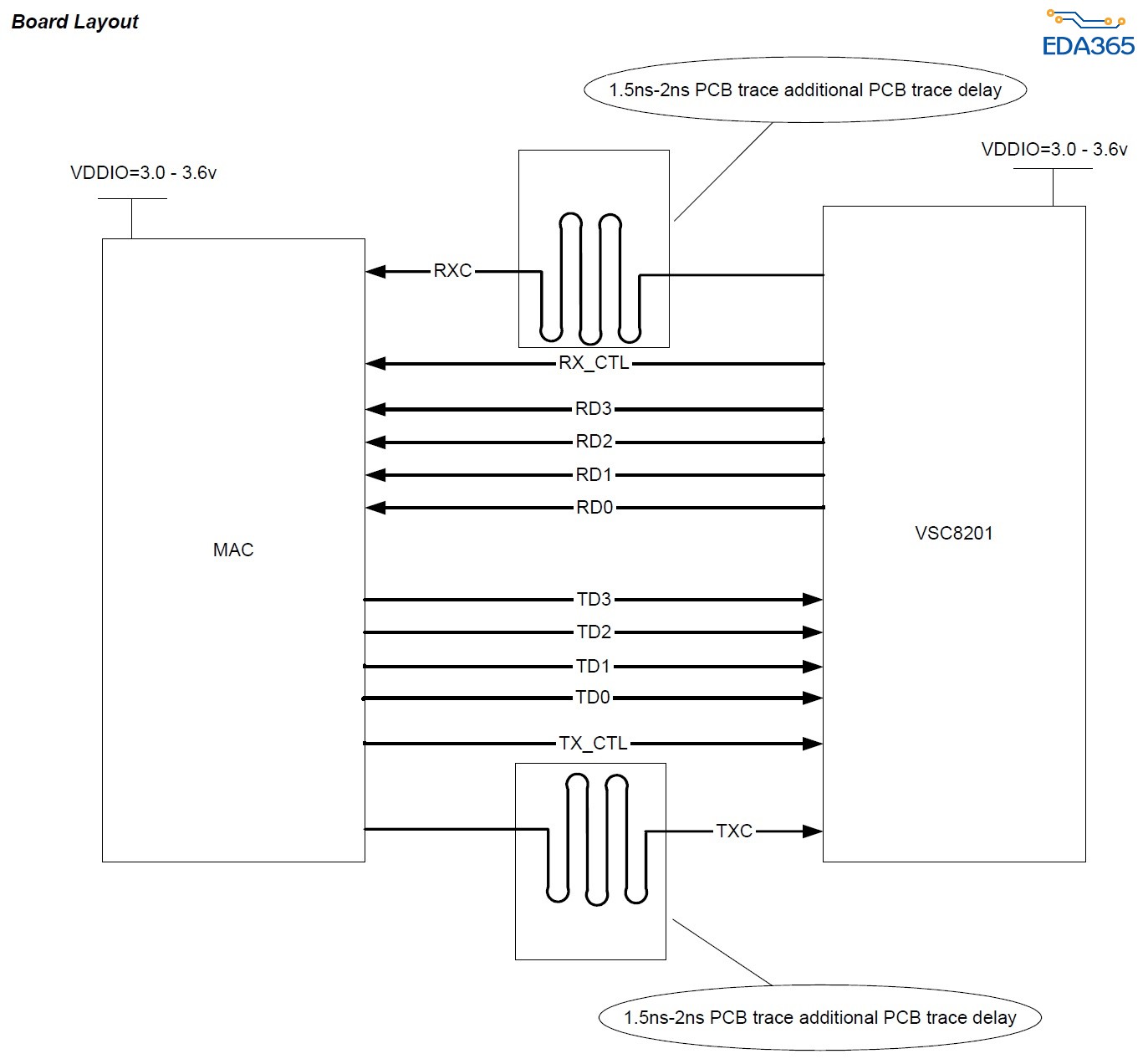

我记得RGMII的clk和data之间 如果在芯片内部没有delay的话,走线好像有一个delay要做的。

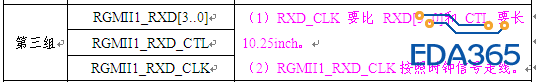

长10.25inch,不可能吧

SimpliPHY VSC8201 PCB Design and Layout Guide

网口的信号没那么严

需要的,2#好厉害!

走线时每4根为一组另加TX_CLK、TX_EN线走在一起,走同层,等长。如:TXD (0-3) 加 TX_CLK、TX_EN

; RXD (0-3) 加 RX_CLK、RX_DV

直接说6根一组,如何?

1,是的,双重作用;

2,原因见下图,收作用RX_CTL is encoded on the rising edge of RXC,RX_ERROR OR RX _DRV is encoded on the falling edge of RXC,发类似,上升下降沿不一样,TXD[0:3],[4:9]就是图上,4根数据线上DDR触发是8位,加上,EN/ERROR就是这么多了,看图;

3,不是你那么算的,RGMII是CK=125M,周期是8ns,DATA=250M,就是4ns,你所有数据上升下降沿都要触发,你把数据中间和CK边沿对齐,那就是数据居中,最理想的是前后各有2ns,然后建立保持时间最少1ns,那么就算数据是最理想的上升下降沿,你也只有1ns的余量可以供你浪。数字时序,不是OK不OK,而是裕量多少,也就是外部干扰了,我还有足够的可靠性可以让设备正常工作,这就是很多PHY的CLK会有个2ns延时的原因,你可以不用绕CLK来保证时序。

那么粗略算以下,一般来说你把上升下降取周期的1/8差不多吧就是1ns,然后信号不理想畸变,那么恶略点你可能只有1000mil的裕量了。然后设计肯定要比理论高,那么就1000mil之内不等长没什么问题,但时序肯定是裕量越大越好,太精确就没什么必要了,在不增加工作量的情况下随意,比如在这里非要做5mil等长,就是闲着蛋疼了,因为这个时序根本不在意那5个ps还是10个ps。拉等长很简单,拉200和25mil都一样的,看你了。

个人理解,仅供参考