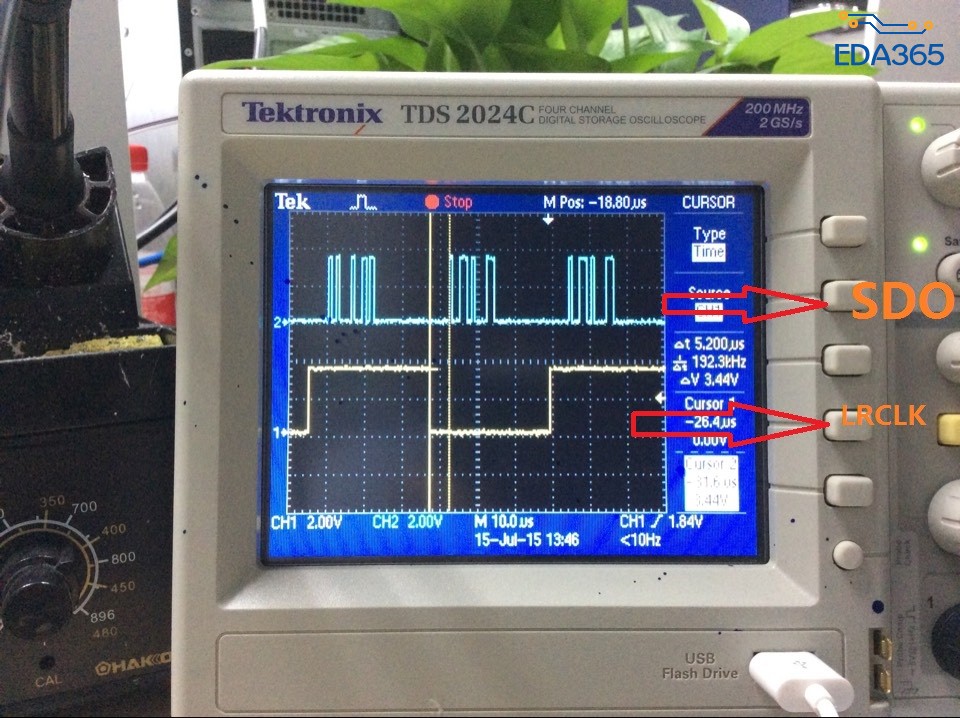

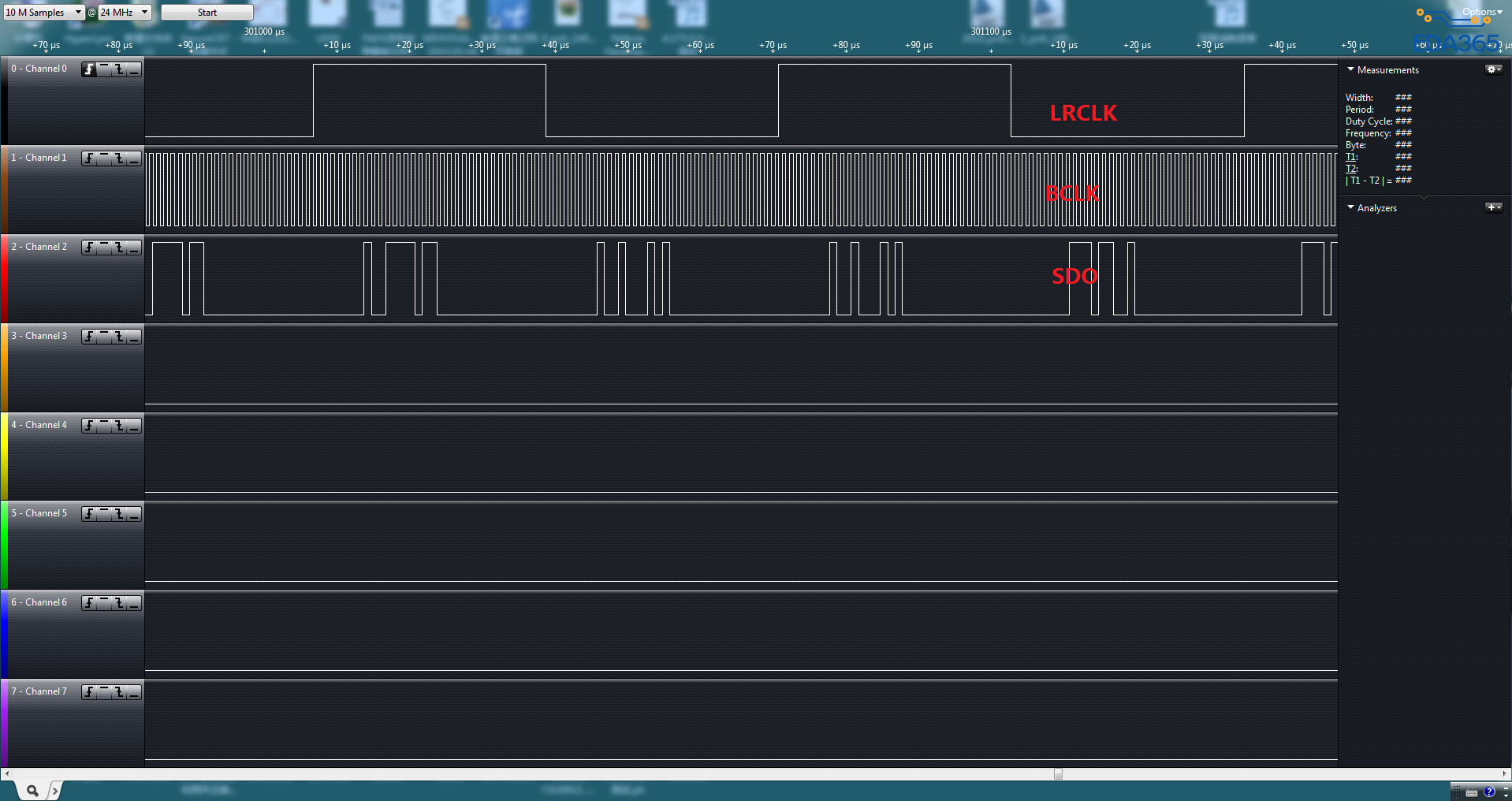

大家可否知道这I2S波形是左对齐,还右对齐?

I2S波形

什么也不说了,看图吧

記得超級狗小编有一份 Intel 介紹 I2S/SPI 格式的狗糧,忘記叫甚麼名稱來著. 有講到不同廠商的 I2S/SPI 格式.

不动,等学习

大多是上升沿触发,就是左对齐。

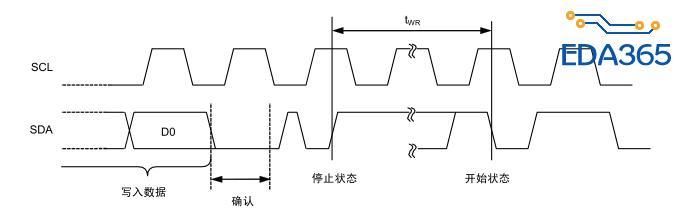

我觉得和这个一样

你看一下吧!SCL端子是串行时钟输入端子,由于是在SCL时钟输入信号的上升边缘和下降边缘来进行信号处理,因

此请要十分注意上升时间和下降时间

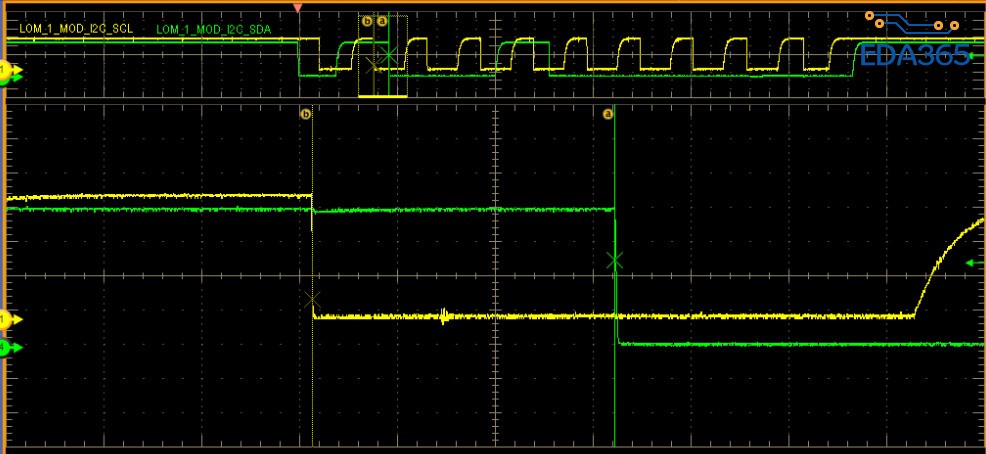

是的,是I2C总线的测量

既然是I2S 波形也应该是SDO 和Bclk 进行采样测量啊,看你的LRCKL 不是采样时钟。[size=14.1666660308838px]你的波形是I2S_FS是frame信号for I2S的。把BCLK 一起截出来才能看出什么模式

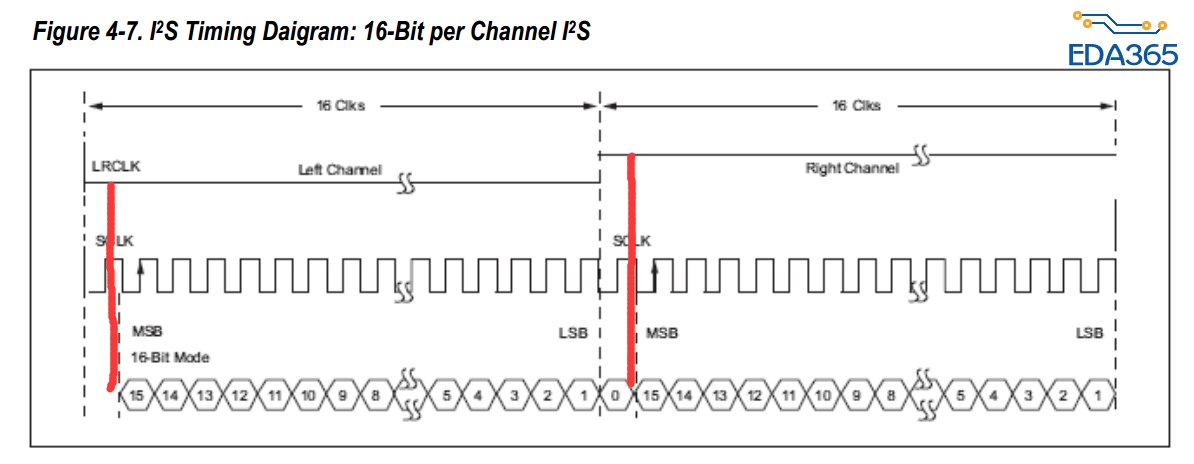

[size=16.2962951660156px]标准I2S:[size=16.2962951660156px]LRCLK的电平变化后,在第二个BCLK的下降沿开始有DATA的MSB数据变化,可使用示波器动态(静态不好识别)看到这个时序;

[size=16.2962951660156px]左对齐:[size=16.2962951660156px]LRCKL的电平变化后,在第一个BCLK的下降沿开始有DATA的MSB数据变化,可使用示波器动态(静态不好识别)看到这个时序;

[size=16.2962951660156px]右对齐:[size=16.2962951660156px]LRCKL的电平变化前,在第一个BCLK的下降沿是最后一个DATA的LSB数据变化,可使用未波器动态(静态不好识别)看到这个时序;

[size=16.2962951660156px]DSP:[size=16.2962951660156px]LRCKL发生一个BCLK的高电平变化后,即连续发送DATA的左右声音数据;

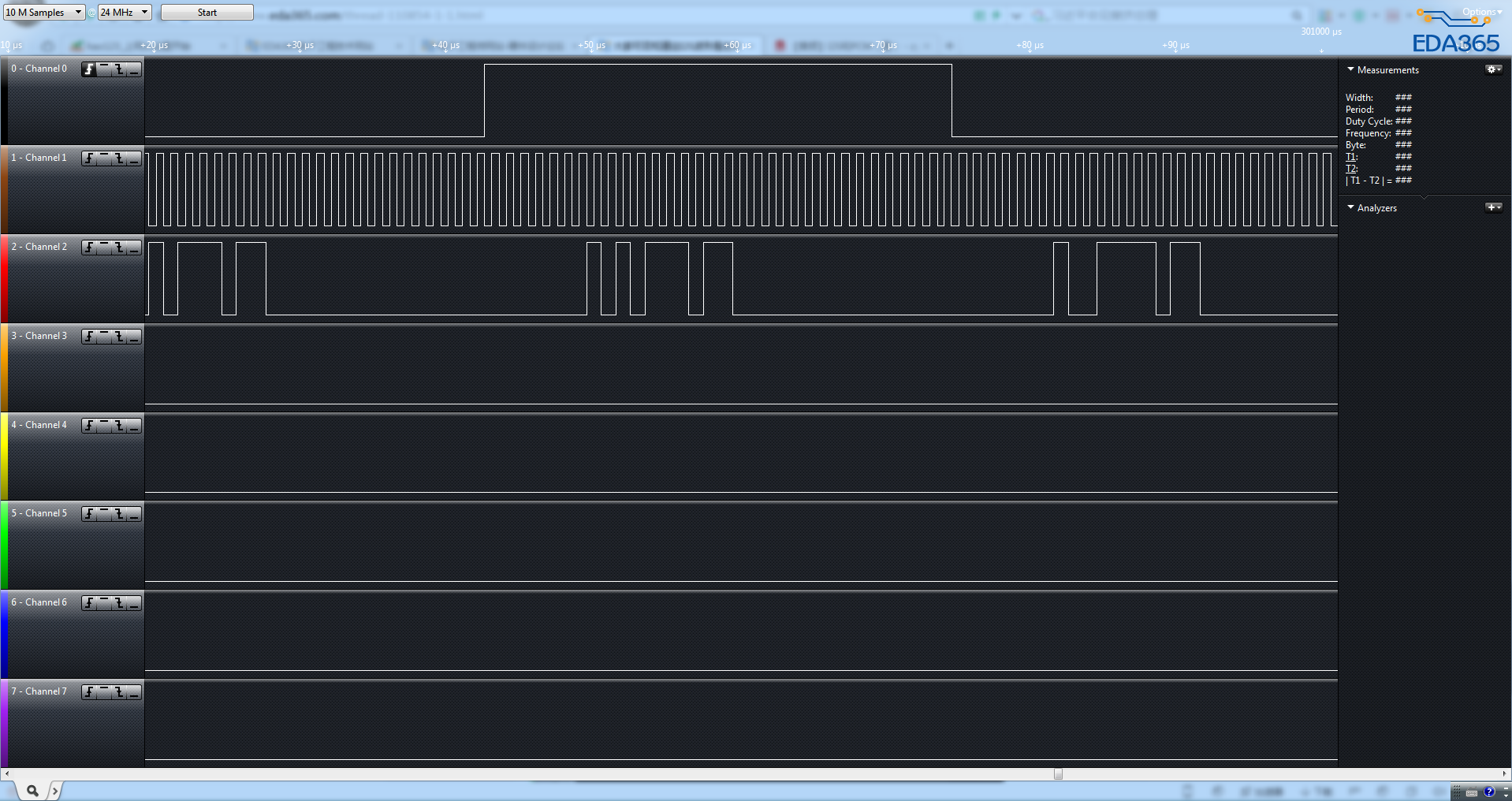

这个是使用逻辑分析仪测的时序波形,看样子是I2S格式,不是左对齐,也不是右对齐方式。

这个放大了,

左对齐:数据采样在LRCK变化后的第一个BCLK的上升沿,对应的MSB

右对齐:数据采样在LRCK变化后的最后一个BCLK的上升沿,对应的LSB

I2S:数据采样在LRCK变化后的第二个BCLK的上升沿,对应MSB

因为不知道数据的MSB是否为0,所以当从波形上无法判断。在某些特殊的情况下也许可以。

LRCK:左右音频的采样率,一般来说:=0代表左声道;=1代表右声道

BCLK:数据的时钟,一般为=2X位数×LRCK