为什么滤波电容的阻抗需小于芯片动态阻抗?

正在读王剑宇老师的《高速电路设计实践》一书,其中关于举例2-12有一句描述说“要求滤波电容阻抗小于芯片阻抗”。滤波电容阻抗和芯片阻抗是并联的关系吗?怎么理解这句话呢?求大侠们指点。谢谢!

我的理解如下:

1 文中所说的,FPGA的IO电流IMAX=0.5A,而电流的波动是50%,也就是0.25A,则我认为他所需要的电流是在0.25A-0.5A之间。

2 文中说的电压的波动取5%,也就是他所允许的或者叫可以接受的电压波动是1.8V*5%=0.09V.

3 这就要求电源在提供波动电流的同时必须满足纹波的要求。

4 文中的意思是通过计算目标阻抗或者叫动态阻抗,来反推电源滤波电容所需要满足的要求。

就是电源阻抗小于目标阻抗。

给力~~多谢点播~~

按照这个人说法就是:电容的ESR和I/O的内阻构成了一个分压网络,但ESR比I/O内阻越小,噪声信号被分压的越厉害,就等于噪声得到了抑制?

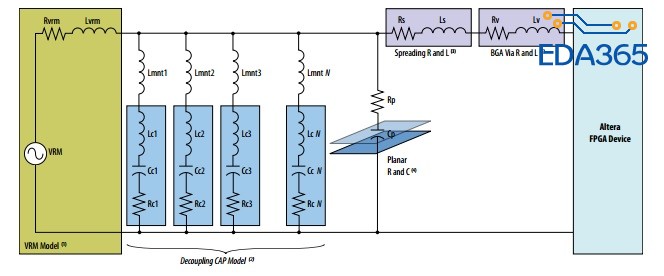

我觉得应该是通过电容网络降低在动态电流变化时,由于电源芯片本身电阻/电感,和走线电阻/电感所带来的压降,使电压更有效地传递到负载端。这个是在Altera PDN工具里看到的一张图,通过电容网络和PWR/GND平面,降低在动态电流变化最大时的目标阻抗,从而降低DC drop。

理解不一定正确,欢迎指正。

说的有道理!

路径的问题,阻抗小,那个回路优先,干扰的纹波直接从那回到地,而不经过IC

理解的非常到位!

就是那个意思,参考BUCK的输出纹波电流和电容DCR的计算。

负载的电流变动,产生了di

而负载的电压波动要求,限制了纹波的要求。

假设不考虑或者电容足够大,忽略电容充放电的影响。

那么就只有ESR*DI的影响,这就是可以看作电源阻抗低于目标阻抗(动态阻抗)的要求。

我觉得从电源芯片这端好理解。不过文中所提到的芯片感觉是目标IC端,它的动态阻抗感觉不在传输路径上,只是接收端。有点不明白文中为什么那么写。

非常感谢!分析的很到位!