高速信号串联磁珠或电容,求教

疑问:1.信号串磁珠会不会影响传输数据?如何选这个磁珠?

2.何时串磁珠?何时串电容?何时什么都不需要?

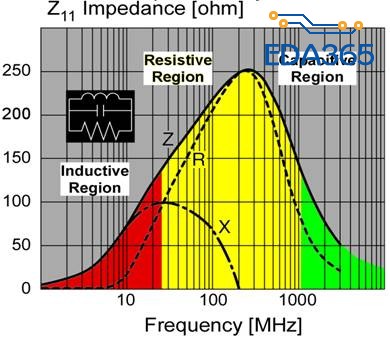

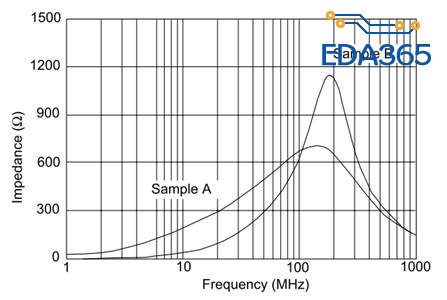

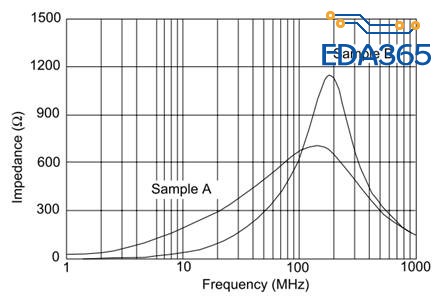

下图是磁珠的频率响应 :

由上图可知,磁珠在低频时,其电抗大于电阻,此时完全是个电感。

在高频时,其电阻大于电抗,呈电阻性, 是个电阻,

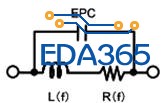

其等效电路如下图,

虽然磁珠等效于电阻与电感串联,

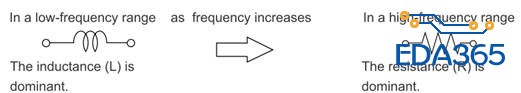

但磁珠对于高频噪声,才有抑制作用,

换言之,我们所要利用的,是磁珠在高频下的电阻特性,

因此在效能上,必须以电阻看待

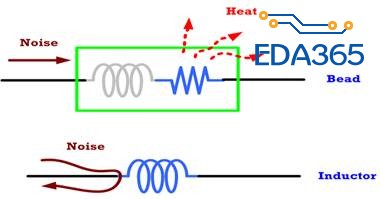

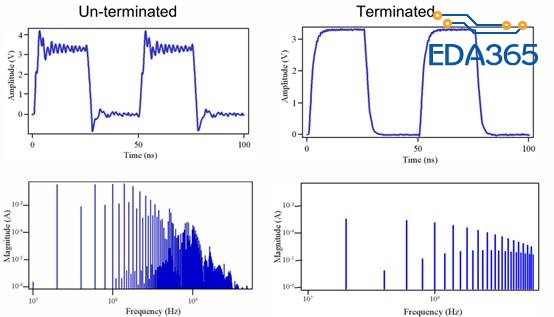

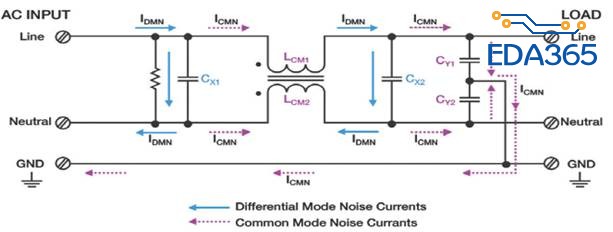

抑制噪声的原理是, 利用其电阻性, 将高频噪声,转化为热能,如下图

虽然一般而言,电感与磁珠可相互替换,

但由于磁珠在高频时为电阻性,能在相当宽的频率范围内保持高阻抗,

因此抑制高频噪声能力,会比电感来得好,所以比起电感,更常被使用于电源走线。

由于磁珠的电感值与电阻值,都会随频率变化,

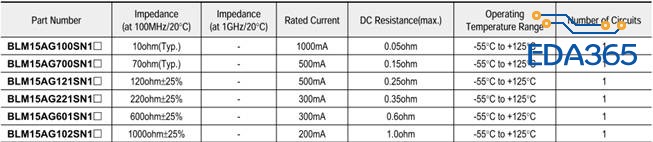

因此Datasheet,都会标注特定频率下的阻抗值,一般都是以100MHz为特定频率。

而由前述可知,在高频时,由于电感值小于电阻值,其磁珠的阻抗,由电阻所支配,

故其Datasheet的阻抗值,其实几乎等同于电阻值,

所以一般说的600R,代表在100MHz下,该磁珠阻抗为600奥姆,电阻值也约600奥姆。

也因为磁珠的电阻值,会随频率变化,因此在挑选时,需注意该磁珠于讯号频率的阻抗值,如下图 :

如果在讯号频率下的阻抗值, 会破坏你讯号整体的终端匹配, 那么波形会失真, 且EMI辐射干扰变大

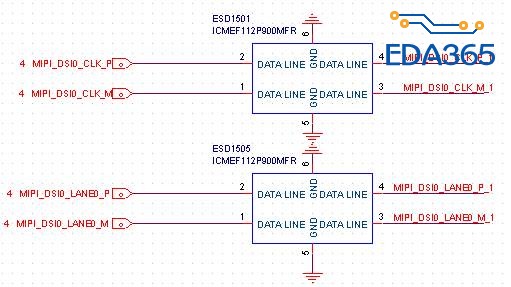

因此一般而言 高速差分讯号 会需要加EMI Filter 来抑制共模噪声

但EMI Filter其组成如下图,多半会以LC电路构成。

而电感会有其内阻 有可能会影响其高速差分讯号的阻抗

同样产生波形失真, EMI辐射干扰变大的现象

所以有些厂商的IC 反而是不建议高速差分讯号加EMI Filter的 道理在此

当然 这时就只能靠Layout去抑制噪声了

再回到这张图

如果是噪声频率下的阻抗值, 那就是越大越有抑制效果

因此以上图为例

Sample A抑制10MHz噪声的能力较佳,

而Sample B比较适用于100MHz ~ 200MHz的噪声频率

虽然噪声频率下的阻抗值越大,其抑制噪声能力越好,

但若阻抗越大,其DCR(DCresistance)也越大,

亦即其信号的损耗,以及电源的IRDrop也越大,故需做一个折衷考虑。

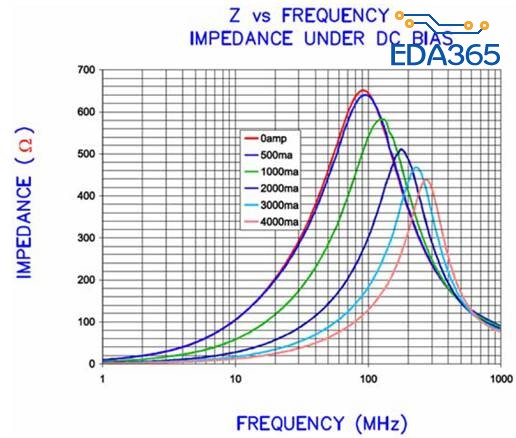

还有一点, 磁珠其规格有所谓的额定电流,来表示所能承受的电流强度,

由上图可知,当流经电流加大时,其磁珠的有效阻抗与带宽,都会跟着下降,

亦即其电阻性频率范围的噪声抑制能力会下降,

虽然因为频偏关系,导致电容性频率范围的阻抗有所提升,

但毕竟我们所要利用的,是磁珠在高频下的电阻特性,而非电容特性,

因此其额定电流越大越好,至少需为流经电流之1.3倍。

但一般而言,额定电流越大,则尺寸也会越大,

但阻抗会越小,因此虽然额定电流越大越安全,

可降低磁珠饱和的风险, 但会加大占用空间,且降低抑制噪声能力,

因此须做一个折衷考虑

因此 你要利用磁珠来抑制噪声 可以! 但要注意

1. 是否会影响讯号整体的终端匹配?

2. 噪声抑制能力够不够?

3. 但噪声抑制能力大, 其等效电阻就大, 会有信号衰减跟IR Drop风险

4. 额定电流够不够? 会不会有让磁珠饱和的风险?

5. 但额定电流越大, 其噪声抑制能力就越差,

别忘了你加磁珠是为了解EMI 若EMI仍无法Pass 那你加也没意义

以上五点 就是你在挑磁珠时 要注意的事项

至于甚么时候不需要?

当然是你完全没EMI问题 一切风平浪静时

能别加就别加了 毕竟由以上5点知道 加磁珠有许多折衷考虑

不是随便摆一颗上去 EMI就迎刃而解

稍有不慎 反而会让EMI更加严重

其他详情 可参照

EDA365藏经阁 › 上集_磁珠(Bead)_电感(L)_电阻(R)_电容(C)于噪声抑制上 ...

EDA365藏经阁 › 中集_磁珠(Bead)_电感(L)_电阻(R)_电容(C)于噪声抑制上 ...

EDA365藏经阁 › 下集_磁珠(Bead)_电感(L)_电阻(R)_电容(C)于噪声抑制上 ...

在此就不赘述

因为如果不编码,势必数据上会有连0或者连1,信号的频率是不稳定的,需要对这些插0或1,保持频率稳定

磁珠的公式,Z=R+JX,不同的磁珠在不同的频点段阻抗表现不一样,可以参考磁珠的曲线图。串磁珠有可以有效的抑制信号的尖峰,防止对外辐射。至于对信号的影响,只要保证在对应信号的频段范围内,磁珠的阻抗足够小即可。

差分信号串电容?你的意思是每根信号上串的电容吗?如果是,应该主要是为了隔离直流的作用,常见于两个不同电平信号的差分传输。在选择的时候要注意容抗,这里特别注意一点就是:容抗的计算不能单看信号的频率,还要看可能出现连续1或者0的周期(换算成频率)。

串电容是隔离直流的作用,但是不一定是所有信号都串了,貌似都是连接器部分需要,是不是通过连接器以后会引入直流,还是什么情况下不需要串就不是很确定了。

串磁珠以前公司做高速没见过,觉得磁珠的话再怎么说也会影响信号质量吧。是不是大家在做接口处的EMI时候都会串磁珠来解决呢?

目前公司有个PCB在接口处串磁珠,电阻,加驱动芯片都试了还是没过EMC。

串电容应该是为了隔直,以前设计过USB3.0到CPU用100nF,SATA接100nF隔直。也有不用的,比如HDMI的信号。

串磁珠,加共模电感,加电容都有用到。

你的不过,看是否是接口处出来的,看看频点。

接口处出来的不一定是出口处的走线辐射,有可能是空间辐射从其他地方耦合过来的

目前EMC那边整改,怀疑走线不顺引起的,要求从FPGA到接口出走线必须很顺,少绕弯,少孔。现在的状况是,这个控制板和哪个板对接哪个板挂掉。

但是其实接口信号都是不是很高速,最高十几兆。控制板有控制阻抗,对接板都没做阻抗。但是信号线走的比较长。

磁珠一般是在电源上的,在信号上的不是太多,信号上有时会并PF级的电容来抗干扰.

学习了

学习了

之前看了一些资料,说磁珠应该是等效电阻和电感的并联,是不是更合理?个人理解,高频时电阻起主要作用,信号能量转化为热能,起到衰减高频信号的作用;低频时电感起主要作用,给信号提供通路。

学习了,赞二楼的资料,超详细

串磁珠选好频率段应该就差不多了,选电容需要信号时编码过的,要不然行不通