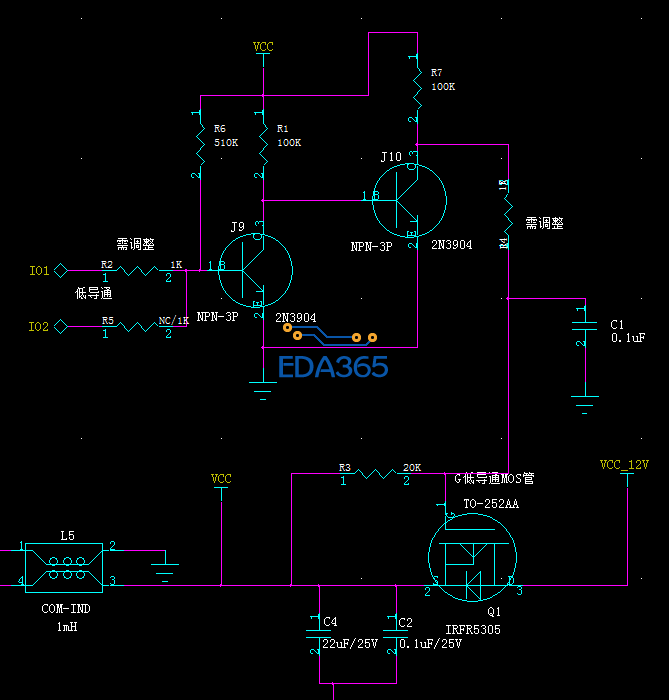

这个电路为什么上电瞬间三极管J9基极有一个低电平

1. J10基极加100nF电容(可适当加大,推迟J10导通)

2. R7改为10K(可适当减小,跟PMOS结电容有关)

3. R6改为100K(可适当减小,加快J9导通)

简单,你把R6去掉,在基极接个10K电阻下来,IO口改成推挽输出

原因就是在上电的时候,被上拉电阻拉高了。

就是要上拉才行的,这个电路三极管J9在基极高电平时,MOS管才会截止,如果低电平,MOS管就导通了。上电瞬间就是因为J9的基极在上电后没有马上拉高,才导致MOS管瞬间的导通脉冲。

哦,不好意思,我先入为主了,sorry。明明看到两级,却无视了,

问下VCC是否是和IO口一路的电源,比如3.3V,如果不是先查下上电时序

如果是,那么把R6改小,比如4.7K。

在R6上并个电容吧

IO1 接的是什么?R5 是不是没贴?

我觉得应该把C1去掉试试,另外R3和R7重复上拉了,留一个就好

关于3.3V时序,3.3V会比VCC晚起来一点点。

IO是通过单片机来控制,是VCC通过LDO降压后给单片机供电的。

但是我做过实验的,IO与单片机断开,直接让IO信号接3.3V和VCC两种方案,接3.3V时,MOS管还是跟之前一样有导通脉冲且脉冲电压有8V左右,但是接VCC,MOS管的导通脉冲电压有时小,有时大。

实际板子上,只有一个R7,R3是没有的,电容也NC的。

R5是NC的,IO1接IO口,现在是直接接的3.3V电源。

小编,图纸画的清晰一点,这样分析问题也好。

你把C1去掉。

C1我已经去掉试过的

按照你目前的实验来看,加快基级的电压了,那你可以把R6减小,并且尝试在上面并联电容,看是否有改善。

小编,你不觉得在导通瞬间,J9和J10是存在导通冲突么?有可能存在J10的基极先高电平,然后MOS管G极低电平,瞬间导通,然后J9基极拉高,J10的基级又变成低电平了,mos管G极拉高,mos管关断。因为R6比R1大,三极管基级对地是有电容的,基级电压其实是一个rc上电过程,那么明显,J9的基极比j10的基极上电晚一点点咯,建议j9的电阻小些看看是不是这个问题。