ZYNQ7020 DDR3

时间:10-02

整理:3721RD

点击:

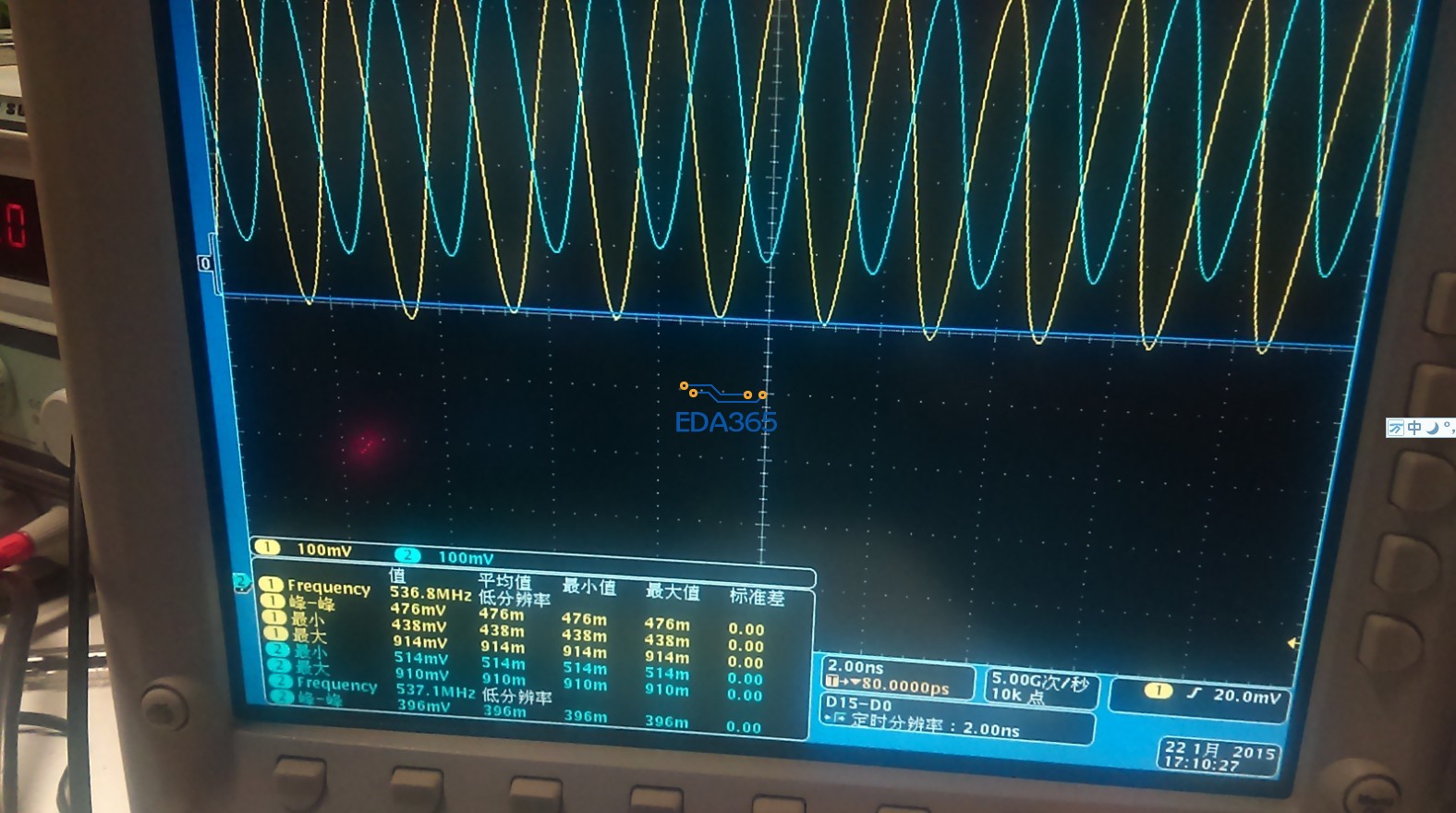

我用的ZYNQ7020 现在DDR3只能跑300MHZ,跑到400MHZ测试改数据出错,不知道为什么,我现在测量DEMO板和我做的板的CLK信号如图片。黄色的是DEMO板的,绿色的是我做的板的,现在软件工程师说我的CLK很差,我不知道这是不是很差!有没有人给我解答,为什么板子只能跑到300MHZ

CLK 黄DEMO绿我的

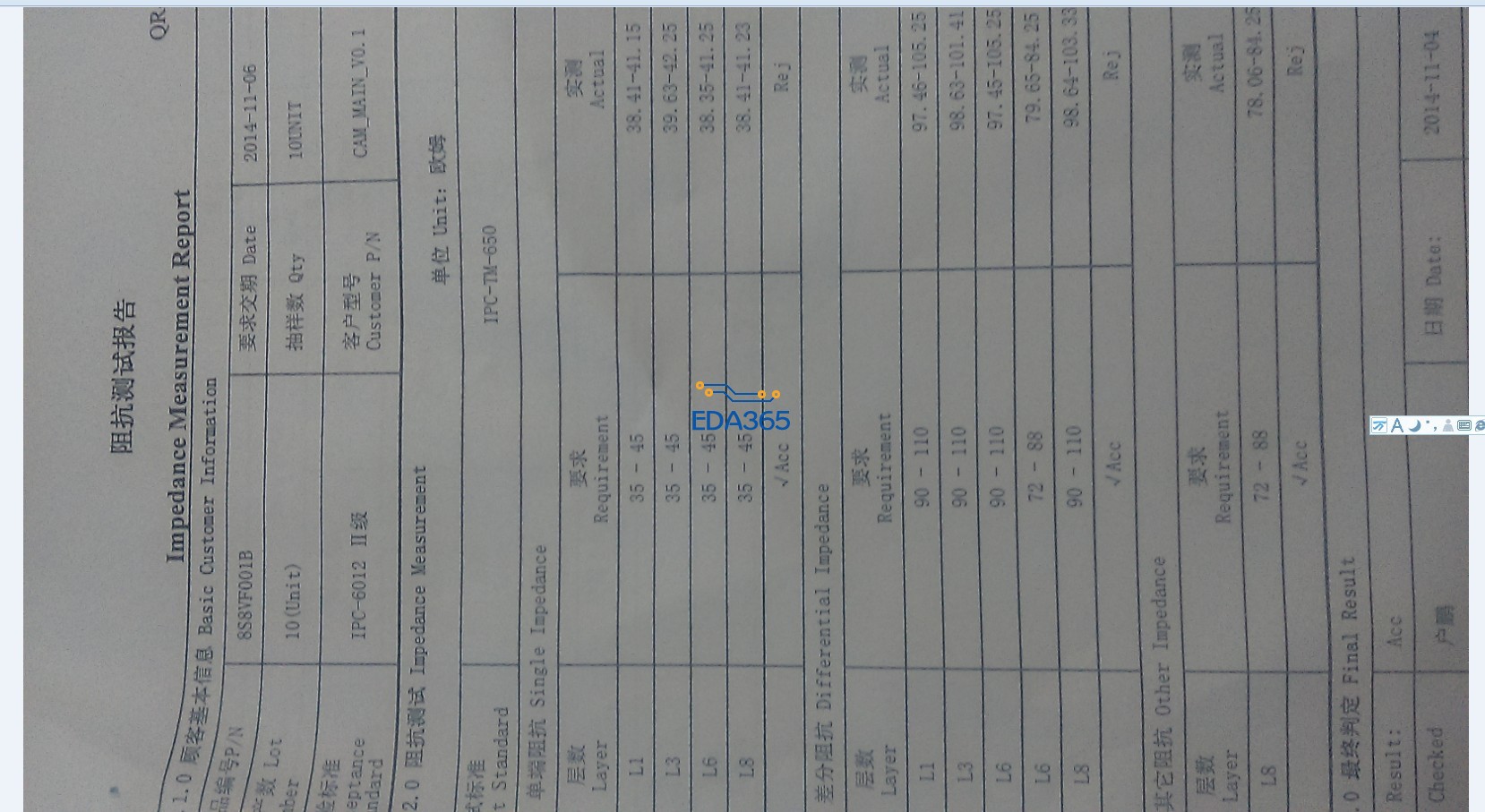

阻抗测试报告

两种地址拓扑都可以。

自已先顶一下

调相位有用吗?

你的DDR最高能跑多高

我现在只能跑300MHZ,跑到400MHZ测试就数据出错

调相位怎么调?

感觉你这示波器带宽不够,都显示成正弦波了,也看不出抖动,过冲等信息。有可能回钩也显示不出来了

2位继续讨论,搬个板凳听讲

刚做了一个XC7Z015-1CLG485C,地址做成T型的,测试下了好像是数据线有警告,使用没问题,(damo板也有警告)。

XC7Z015-1CLG485C

是否可以通过软件来调高运行频率?

我的板子还没贴片,等贴片也看看能跑多少

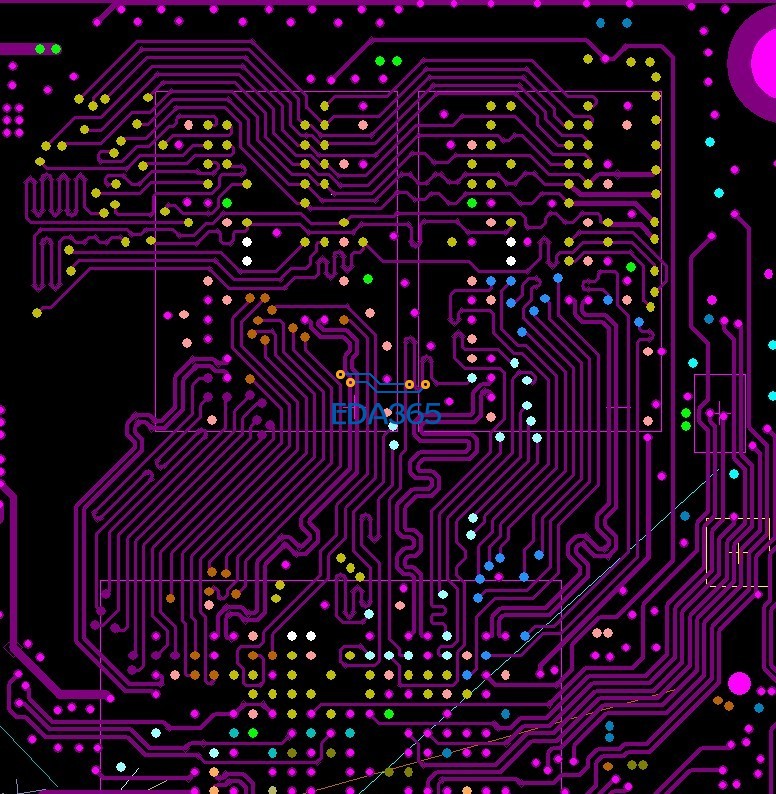

从你板子的走线来看,似乎问题不大,不知道层叠是怎么做的呢

软件那边有根据你的走线来做内部延时调试么,我之前遇到这样的问题,跑800就是不行,降到400就是可以,偶然间我说了我修改了ddr3布局布线(板子结构改了),软件那边才想起来让我走线长度(已经做好等长了)重新发给软件那边,他们重新调了参数,然后就没问题了。

把DDR和CPU模型和PCB叠层和文件给我帮你仿真一下,看看结果