聊一聊源端匹配和终端匹配,请大神们指点!

我的理解

源端匹配-----因为驱动源的内阻小于传输线的特征阻抗,所以要在源端串一个电阻,来使传输线认为驱动源的内阻和其内阻相等,这样整个系统(从驱动源到传输线,再到负载)的阻抗才是连续的,才不会产生反射。

终端匹配-----因为负载的内阻小于传输线的特征阻抗,所以需要在终端串一个电阻,来使传输线认为驱动源的内阻和其内阻相等,这样整个系统(从驱动源到传输线,再到负载)的阻抗才是连续的,才不会产生反射。

我同学的理解:

源端匹配----是为了防止反射回来的信号,干扰驱动源再次发送的信号,才需要进行源端匹配。

终端匹配----他没有发表意见。

公司仿真组同事意见:

源端匹配----他同意我的观点

终端匹配----他不同意我的观点,他认为终端匹配必须是并联电阻到地,因为,他认为负载阻抗始终大于传输线阻抗。

请各位大神们给分析分析,谢谢!最好写出自己的理解,不要给个网址,或来一句“百度,谷歌”什么的!

源端匹配,你的同学理解是对的,是用来消除二次反射的。

终端匹配,理论上可以消除反射,但实际是做不到的。

那请问,我理解的对吗?请给详细说说呗!谢谢

我不敢说你的理解不对,只能说不全面。以并联终端匹配为例来说,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,以达到消除负载端反射的目的。

在网上,搜到一篇仿真的文章,该文章描述了,源端串阻对终端信号的影响。请各位看看,谢谢

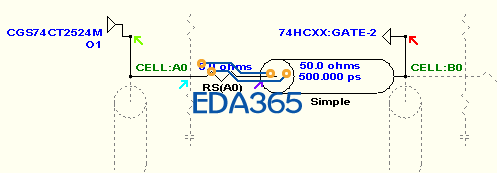

打开自带实例中的Ser_ibs.tln

图中的CGS74CT2524为output,74HCXX为input,它们都有各自的ibis模型。

源端的端接电阻RS为0欧姆,传输线为50欧姆。

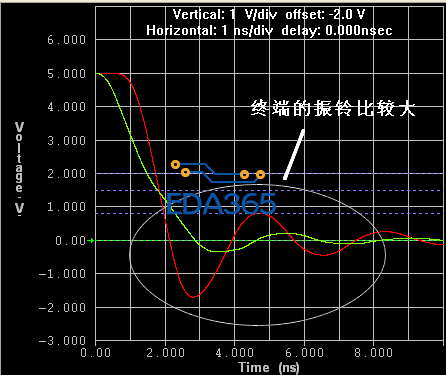

先运行仿真一次,IC model的速度选为Typical,它表示上升下降沿的速率。Fast-Strong最快,Slow-Weak最慢。

运行之后的结果如下,图中红色的波形为输入端74HCXX的下降沿,振铃比较的大:

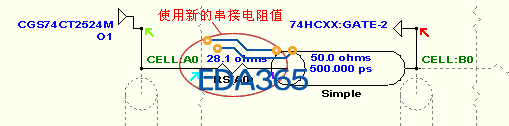

修改源端端接电阻改善波形的方法

HyperLynx带有智能端接分析的功能,菜单Wizards->Run Terminator Wizard运行之后,给出了推荐的电阻值28.1欧姆

设置完成之后RS的阻值已经改变了

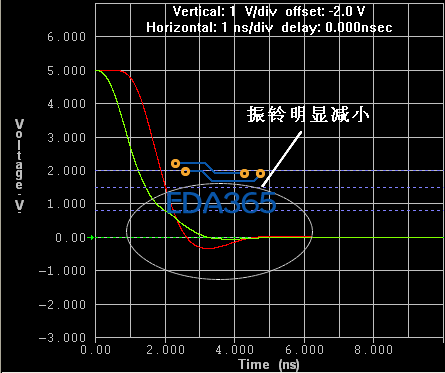

再次运行仿真,结果如下,终端的振铃显著减小。

针对你的理解说下吧:

1.源端匹配。你是说为了防止反射;当更具体来说,是防止二次反射。所以你的理解和你同事的理解并不矛盾的。

2.终端匹配。仿真组的同事说得有点绝对了。众所周知,做阻抗匹配就是为了是阻抗连续,所以终端究竟是串联还是并联,还是需要根据负载大小来定的,只要保证阻抗连续就可以了。

请问:“终端匹配,理论上可以消除反射,但实际是做不到的”,这个里面终端匹配为什么实际做不到消除反射?

其实具体的情况比较复杂,但是实际上理解的话要抓住几点:

1,不管串联和并联都是一种手段,目的是为了让信号更好的从源端到终端;

2,一般来说,源端的输出阻抗一般都不大,而且随着高低电平不同阻抗也不一致;而终端接收端的阻抗一般很大,所以两者不是由三者的阻抗关系决定的;

3,假如没有电阻,信号从源端出来后,幅值会降低;而在到达终端时候由于近似开路,信号又会接近全反射;

4,假如源端30欧,传输线60欧,终端1M欧。那么如何看待在源端串一个30的电阻和在终端并一个60欧的电阻又和区别? 假设信号是3V-0V

前者信号在传递过程中,从信号源出来,由于分压效果,会以1.5V继续传播,到终端全反射,1.5+1.5=3V,信号回复,但是反射波形会传回源端,这时候串联的电阻会把这个波形吸收;

而后者的信号则是以3V传递到终端,然后全反射,但是终端并联了个和传输线阻抗一样的电阻,这是终端的电阻就把这个波形吸收

但是串联对于普通信号容易实现,简单,PCB走线也简单,并联不仅布局麻烦,而且会有持续的直流功耗,所以一般不用,DDR上可以看到。

另外“终端匹配,理论上可以消除反射,但实际是做不到的” 应该欠妥吧,不然DDR的设计不就SB了么?我实际在NANDFLASH和DDR的总线上测试过终端匹配,效果很明显,所以搞不懂这哥们是从哪里看到的这个理论

消除是指完全没有,全部除去的意思,没有哪种匹配能够100%将反射消除,只能将反射控制在可接受的范围内!

消除是指完全没有,全部除去的意思,没有哪种匹配能够100%将反射消除,只能将反射控制在可接受的范围内!

好吧 你赢了 的确是这样 不过这个地方不需要咬文嚼字吧

好比说如果有什么方法可以把波形变成完美的方波 信号完整性的工程师就失业了

呵呵,没有谁输谁赢。可能是我表达的不清楚。

思路很清晰啊

另外我再加一句,例子中并联匹配的情况,从源端到传输线端的电压已经不是3V传输了,而变成2V了,所以即便到终端匹配后直流电平也达不到3V了。

好的,多谢!

是的 搞忘了 终端匹配要降低电平的