请教MII的由来!

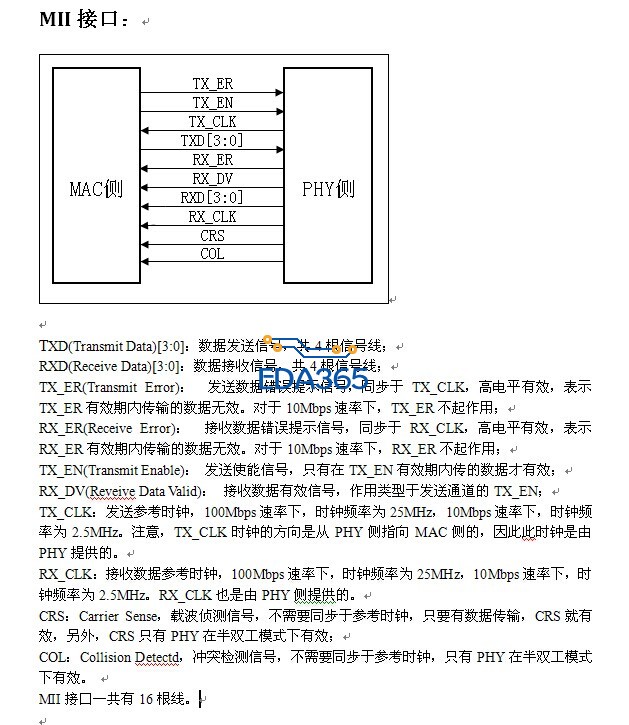

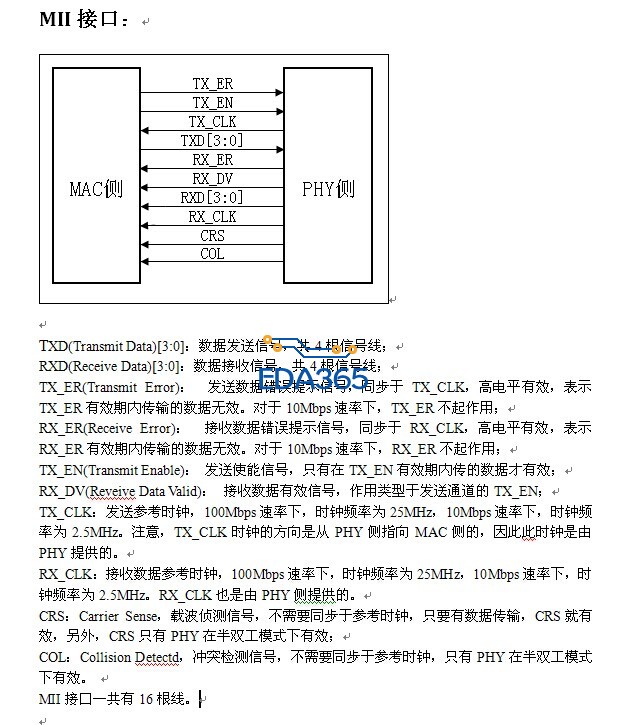

MII ,或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。数据接口包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号。管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。MII (Management interface)只有两条信号线。

百度,谷歌来的快,直接复制!

上不了谷歌的童鞋们,可以试试这个 http://www.gfsoso.com/

百度真心不好用。

谢谢回复!您说的很对,不过,你只说了一个大家都知道的定义!嘿嘿

同意你的观点,百度确实不怎么好用!

谢谢你的回答!不过,我想知道,MII的应用环境,以及什么时候需要进行端接匹配,用什么样的匹配?匹配电阻的阻值如何计算?PCB走线有什么要求?谢谢,嘿嘿!

MII的应用环境?----不太明白你需要知道些什么。

什么时候需要进行端接匹配?

当信号大于100MHZ或者上升沿小于1ns或者你没有把握的周期性信号一般都需要端接。MII的接口除了CLK其他的可以不用端接。

PCB走线要求:

信号分类组包,CLK串联电阻靠近远端并且单独包。

看了你的回复 你对大家的回答都不满意 但是你的问题根本就什么意思表达不清楚 如何求解?

呵呵,没有不满意!可能我的问题确实有点模棱两可!对不起各位啦,再重新问一下吧!

问题1:MII的由来,就是MII是由什么发展而来的或者是MII是因为什么而提出来的,因为MAC与PHY需要互联,还是因为MAC与PHY之间的互联速率提高了,而原有的协议不能满足要求,才提出MII这种接口?

问题2:MII接口PCB走线时,需要注意哪些因素,PCB走线的距离是多少?Mii接口是否需要源端阻抗匹配设计,如何进行阻抗匹配?谢谢

1,个人觉得 这应该缘由于通信协议 以及OSI模型, 就是说基于MAC和PHY的互联需求而规定的 MII本身就由于现在通信速率的提高一直衍生出新的内容 MII、RMII、SMII、GMII、RGMII、SGMII、XAUI等等一系列

2,按理论来说 MII应该等长,PCB单端信号60欧匹配,走线长度限制当然越短约好 但一般来说,没见过谁把MII走到1500mil左右以上的,所以等长什么一般完全忽略, 匹配阻抗就行了,不过具体阻抗要看芯片需求 不一定是精确的60 衍生的高速MII系列 就肯定随着速度越来越高 要求就越来越高,但由于采用高速差分结构,要求虽高,操作起来也没想的那么复杂了 到后面的QSGMII,XAUI就不解释了 弄不好就出问题

个人理解,仅供参考

眾人息怒!樓主沒有不滿意大家的答案,只不過他問的是 MII 的由來,而不是 MII 的定義。

這也是為什麼,我也搜到百度等網站的說明,但不打算貼出來的原因。

其實,關於 MII 的由來,網路上的討論並不多,但如果去仔細思索 MII(Media Independent Interface)全文的涵義,樓主會知道這個界面是怎麼來的。

樓主您懂的!