ddr3 vtt端接问题

时间:10-02

整理:3721RD

点击:

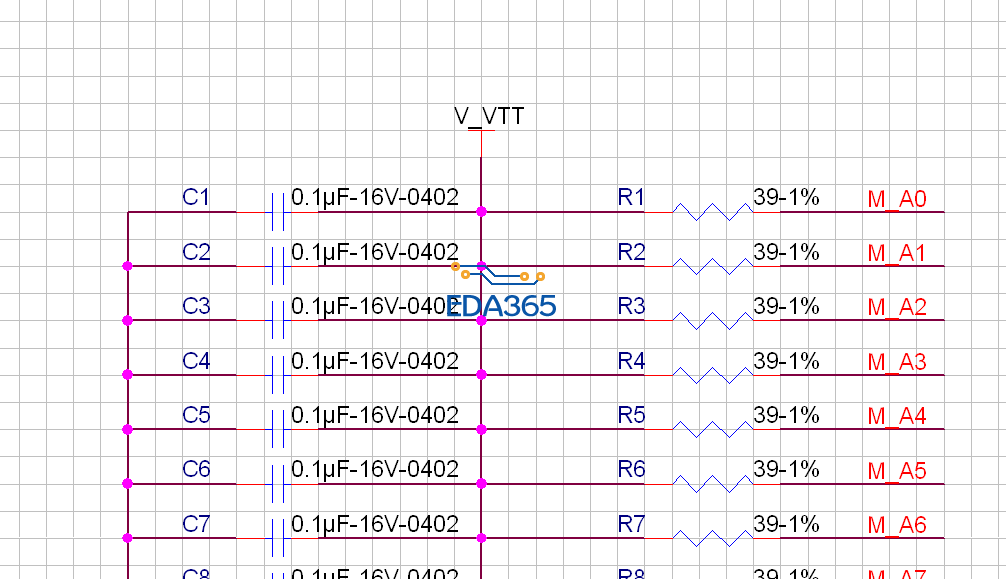

请问ddr3这两种端接方式有什么不同?

vtt上拉

节省了电阻,但是需要单独的vtt芯片供电,其实是增加了成本

下面一种好。

请问ddr3这两种端接方式有什么不同?

上圖直接以電阻分壓來取得 0.75V 的端接電壓 (端接電阻=50 Ohm),下圖則要另外一組 0.75V VTT電源供給 (端接電阻=39 Ohm)。

还是觉得没说透,design guide上这两种都出现过,vtt应该比用1v5分压电压纹波更小,电压更准一些。

老板应该会比较喜欢第二种,节约成本

戴维南并联终端匹配和简单的并联终端匹配方式之区别。貌似信号完整性一书上有介绍过:

两者都可以实现信号的终端匹配目的,但是前者还相当于一个上拉,一个下拉,提高了系统的噪声容限,同时可以改善信号的质量,使得信号的摆动缩小,而且电平不匹配的时候也可以用这种方式。但是很显然的,这两个电阻无时无刻不需要功耗,故而有些环境不适宜,而且,2>1,在LAYOUT时候会加大处理难度,处理不好,反而会有相反作用,目前较少看到此方式。

后者只有一个上拉,会使信号的逻辑高输出电平下,降低了负载输入端对噪声的免疫能力,但这种设计较前者更为简单,尤其现在高密度时代………………自己查吧,上班了