FPGA之管脚分配@DDR3

时间:10-02

整理:3721RD

点击:

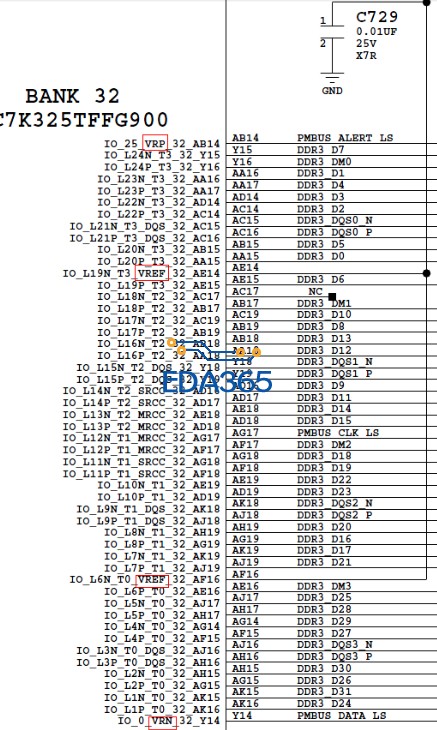

项目遇到了个问题,各位大侠看这里!FPGA选用的是Xilinx公司新出的Kintex-7系列FPGA,该FPGA有3个HP BANK用来给DDR3分配管脚,每个BANK是50个I/O,现在想要实现的是每个BANK各接16bit的DDR3,现在算了下DDR3需要47个I/O,而每个BANK中有2个VREF管脚,和一个VRP、一个VRN。这样的话,就得47+4=51>50了,想问下这个VREF能不能用作普通I/O?还是这个VREF必须有作他用?

这个是开发板上的对应HP BANK原理图!

当然是不能用作IO,必须要接参考电压的

没用过 FPGA,围观下

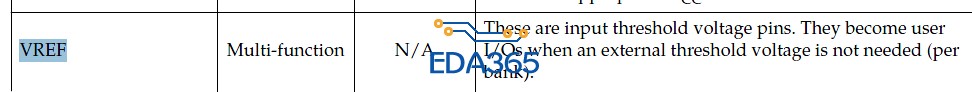

方法一:找到该芯片的管脚介绍,找到这个pin,看看有没有普通IO功能。

方法二:找你们FPGA工程师,让他帮你把这个PIN配置成IO口,他会告诉你可以还是不可以的。

感谢您的回复!呵呵,是学校拉的项目啊,木有FPGA工程师额。是可以当普通I/O用,就是不知道会不会有影响。

一般可以用,可能延时之类的会大点,或者之只能作普通IO

想Altera 最好就是DQ功能的接DDR的DQ,DQS接DQS 这些多是专为DDR优化的,里面带DDR功能,DDR功能管脚

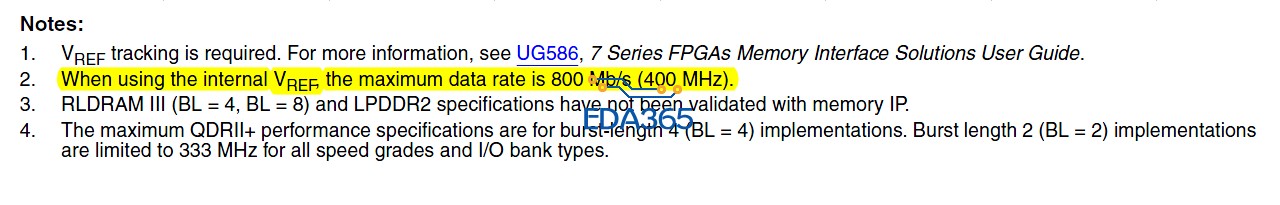

刚查了手册,VREF管脚是可以用作普通I/O的,只是对应的DDR3传输速率最大只能达到800Mbps,问下这个Internal Vref指的是FPGA编程时候的配置吗?

这个不清楚,按意思VREF应该可以内部哪里设置一下,或者外部VREF输入进去。

就像AD的参考电压一样,有的可以内部的参考,或者外部输入进去,这个文档找找应该能找到。

问了下我们的FPGA工程师,当作为VREF时需要外部供电,DDR只是数据存储,不像AD带有转换所以内部有可能含有内部参考。但DDR接口一般不会含有内部参考,所以需要外接。