DDR3時鐘匹配

时间:10-02

整理:3721RD

点击:

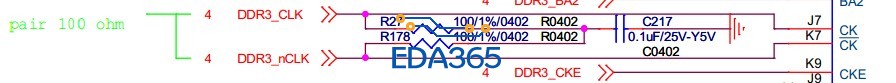

請問大家,DDR3的差分時鐘的匹配是怎樣的,看過不同的電路路,各有各的說法。

有很多种。其实说白了就是源端匹配,末端端接。

看情况而定的。

源端匹配有:

单根并联22ohms左右的电阻。这样会拉低信号幅值但是可以减少反射。

两线间并联100ohms电阻。这样会拉低信号幅值但是可以减少反射。

并联容抗为100ohms的电容。不拉低幅值,稍微减缓上升时间,减少反射。

末端匹配有:

T型匹配,pai型匹配,还有图中这种T型的变种。很多。

最简单的就是两线之间并联100ohms电阻或者单根50ohms电阻上啦到VTT。

根据驱动器的驱动能力仿真得到的结果比较靠谱。

匹配有阻抗匹配和时序匹配。阻抗匹配,首先时钟线走线要控制好差分阻抗,通常100欧,再就是会有匹配电路,一般都是末端匹配,如你图中的阻容器件需放到链路的末端。对于时序匹配首先同对两根线要做等长,时钟和地址、数据线的时序关系要看芯片资料来定,不同芯片之间会有些差别

这个图用100欧?应该是50欧啊

用什么仿真软件比较好!

是个时域的仿真软件都可以··最简单容易上手的当然是hyperlynx