继电器控制电路问题,求解

时间:10-02

整理:3721RD

点击:

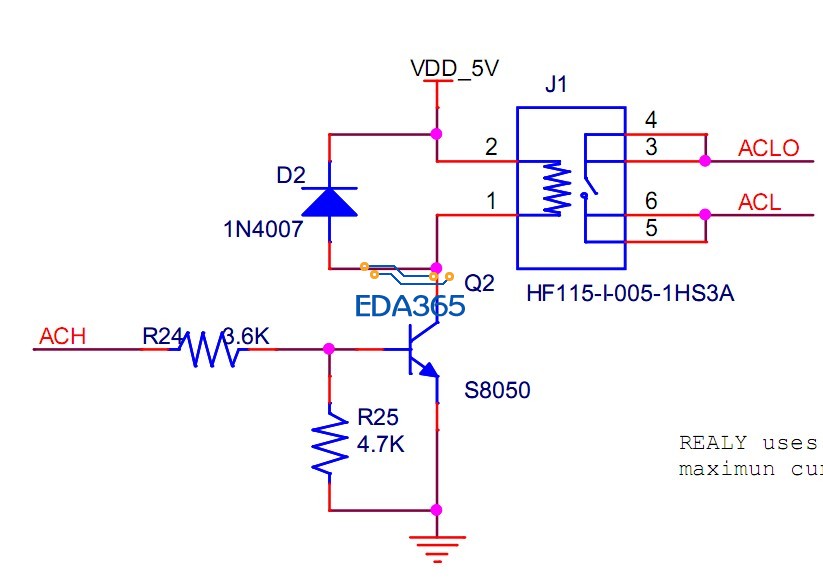

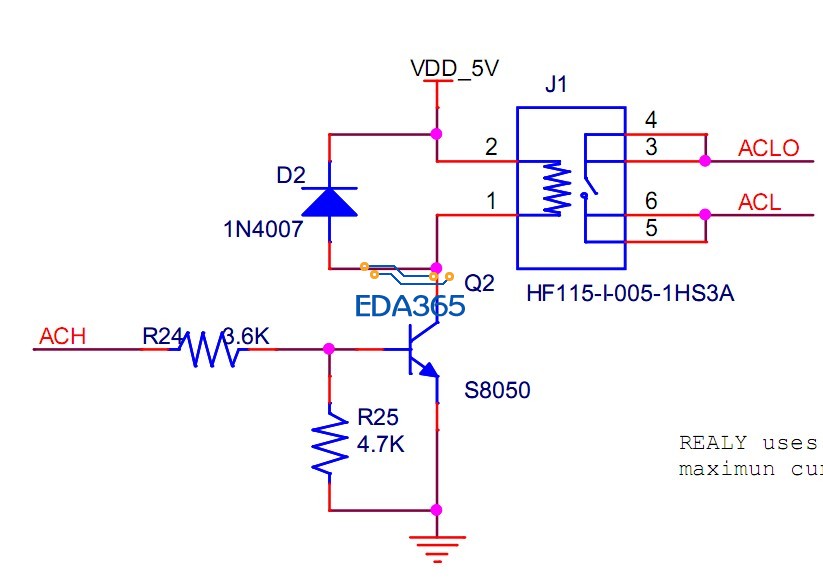

想用一个IO口通过8050控制一个继电器(80ma电流),其中IO的逻辑高电平为3.3V,如图所示,当IO输出高电平,继电器能够闭合,但是会导致整个CPU的IO输出管脚的逻辑高电平被拉低到2.2V,如果增大R24至10K,逻辑高电平输出增加到2.6V,求解,什么情况?

这个是CPU的IO口驱动能力不够所导致,仔细看下CPU的驱动电流最大是多少,然后根据驱动能力大小,选择合适的驱动电阻,实在不行就要考虑用MOS管了。

npn三极管的漏电流所导致,建议用n-ch mosfet或p-ch mosfet +npn

R25改为3.3V上拉,问题已经能解决。

上拉必导致上电顺序不对!

可以将R24,R25的电阻适当改小点。一般,在控制系统使用继电器,最好加一个光耦前后隔离。

MCU低电平驱动能力比高电平驱动能力要强很多,因为他的高电平其实是靠内置的上拉电阻大约4.7K拉上去的,所以最好用低电平来驱动...

研究了几天,认为在IO置高电平之前,三极管的C极电压为近5V,三极管导通瞬间C极对B极压差大于0.7V,导致BC之间导通使得B极与R24连接点电压被拉高,使得R24上电压高于IO口的高电平,使得CPU处于栓锁状态,引起CPU逻辑电平工作不正常!

感觉是CPU的IO配置不对或者是IO的驱动不够,不过一般驱动的可能性不太大,CPU IO配置不对的可能性会大一些.

以上情况CPU采用的是TI的MSP430F5172单片机,试验发现改用MSP430F4152单片机后同样采用3.3V供电,输出正常,IO也没有被拉低。

IO驱动能力问题 还有 你这个电路 上电继电器就会开关一次吧

应是驱动能力不够,R24电阻大了,我用STM32F系列芯片做时,没出过这个现象。