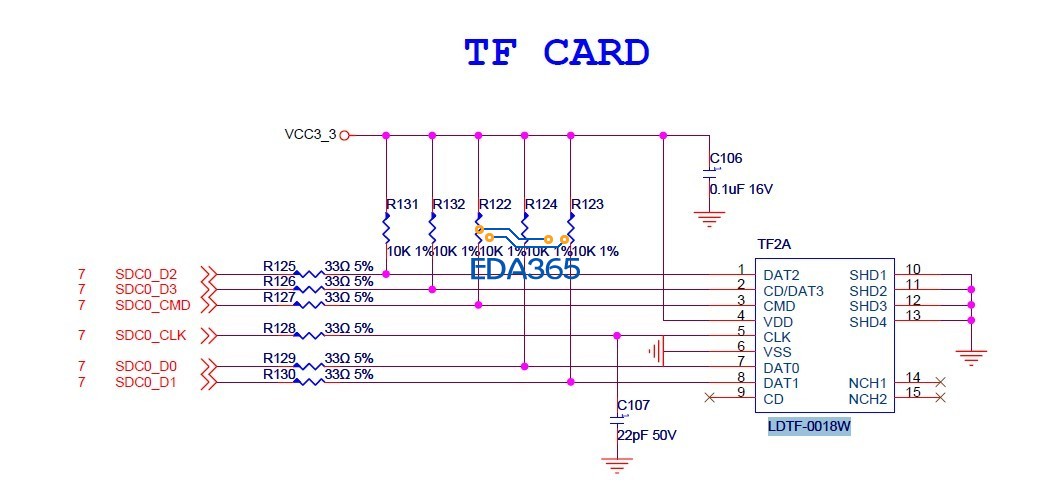

TF卡上拉电阻问题

时间:10-02

整理:3721RD

点击:

TF卡中,连接电源的电阻作用是上拉吗?具体是怎么工作的?

可以看看SD卡的相关资料哦。它的数据线是需要上拉的(一般都是采用10K电阻)。时钟线就不需要的,一般的话,都需要加点TVS管,用来防止ESD。 33R的是防反射的。还有为什么你的CD脚不接?那么你可能就不支持拔插检测了,除非采用软件查询的方式。

CLK脚为啥接了个22pF到地。

同楼上问,会不会使时钟信号变成一条线啊。

这个和T卡的SDIO接口协议有关系,协议要求host必须提供上拉,但是有些芯片是将上拉做到内部的,所以外部不用再加。

CLK 的电容作用是调整波形和相位做用,串的小电阻为 防过冲的而加的,

不是很明白调整相位的作用是?

clk接阻容不是降干扰的吗

我是新手,上边的电路图是师傅做的,不懂,所以来问下,谢谢好心人

谢谢,说的很详细

我不懂,是来学习的

CLK接电容降低干扰用。我猜是由于排板中,CLK线走线比较远,所有此信号线上有干扰。此RC滤波可以很好的滤除一些干扰。

加上拉,提高带负载能力,加电容,降干扰

上拉是数据必须满足数字信号的规范,串电阻是阻抗匹配,电容是改善过冲,如果电路波形可以的话,电容可以不用加,这个跟你的 f_CLK 有关。

CLK的电容可以看成是种冗余设计,CLK波形OK的时候可以NA掉,加上可以改善波形。