DDR2数据线顺序

DDR2用的是NT5TU32M16DG,ARM用的是ST的STA2165。

ARM与DDR2之间的数据线顺序,一开始画原理图时按照对应关系来接的,DDR2的DQ0接至ARM的DQ0,以此类推,DDR2的DQ15接至ARM的DQ15,也按照这个连接关系布PCB,板子出来后调软件发现DDR2这块怎么也调不通。

后来检查原理图,发现推荐的原理图DDR2和ARM的数据线顺序并不是一一对应的,而是ARM的DQ[0:7]对应到DDR2的DQ[8:15],ARM的DQ【8:15】对应到DDR2的DQ[0:7],而且两个字节内的线序也是打乱的。

跟ST原厂的沟通了,说我们之前的接法是错误的,必须按照他们推荐的顺序接,

在网上查了,有人说为了便于PCB走线,数据总线可以乱序相接,但为什么我按照DDR2的pin脚定义顺序接就不行呢?哪位大侠能帮忙解释一下原因,先谢谢啦!

字节内的顺序更改是不用改软件的,但是字节之间的更改是需要软件做相应的改动的,也许是ST考虑这样改动layout会比较顺,也许真的是PIN MAP错了,不过后者可能性好像不是很大,如果都知道是错的,肯定是要改的啊。

凡事没有决对,只是原厂不乐意帮你改。评估一下,是新做板划算还是请他们帮改一下划算。

无图无真相,先把图贴出来

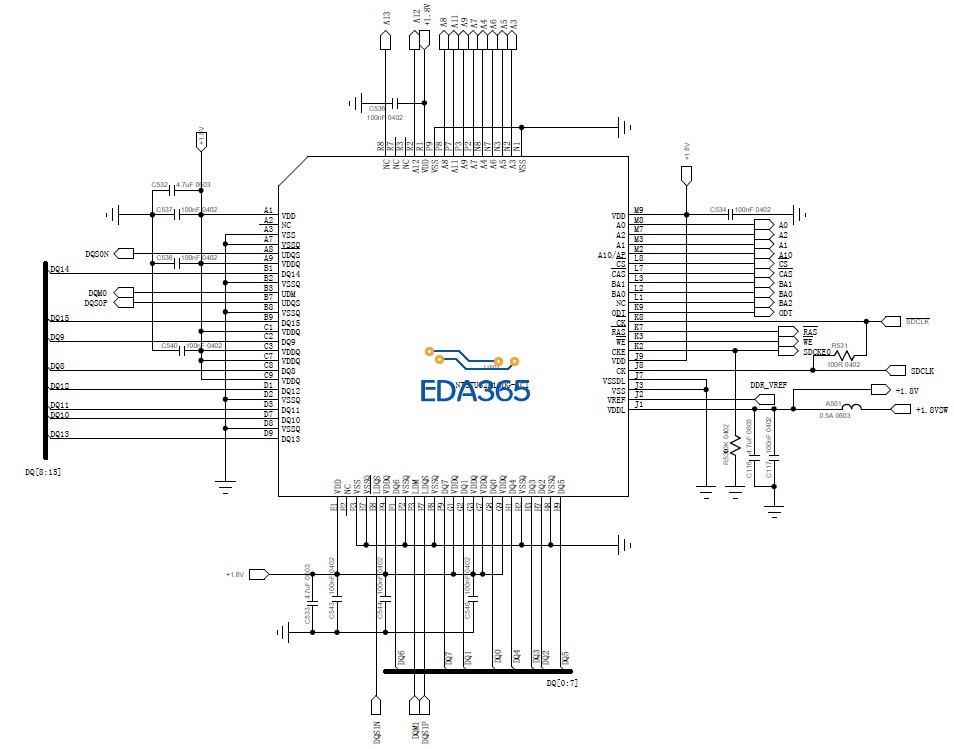

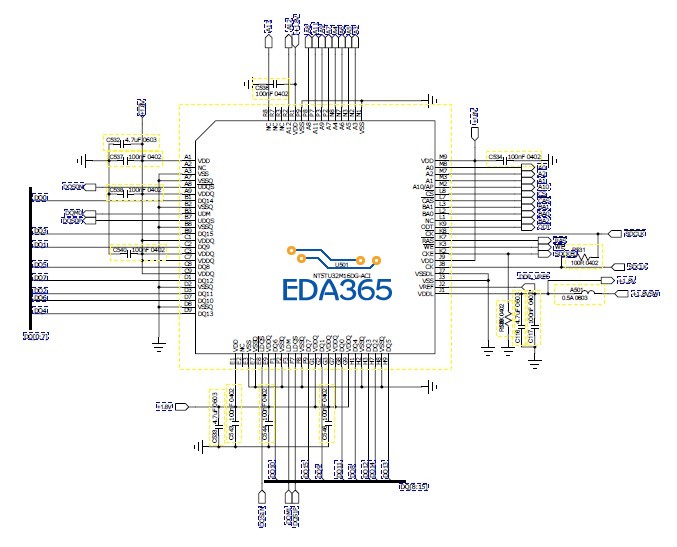

fig1是原来的图,fig2是ST推荐的图。

fig1

fig2

你出的图都没法看清。如果真是高低位接反了,就找软件改改DDR驱动吧。

问题是ST的人说改软件不行,必须按照他推荐的顺序接,不知道什么原因。

字节内是可以任意打乱的,这是因为字节是最小存储单元,D0~D7(或D8~D15)8根线按什么顺序存入,那么当按相同的顺序取出时,取出的字节当然和你存进去的字节一样的。

D0~D7和D8~D15两组对调,也许人家原厂的程序是必须这样的呢。既然原厂说是对的就是对的。

估计原厂为了显示自己的权威性,不想改软件。

这种情况,楼上有兄弟说的对,就是软件驱动的逻辑关系与硬件的物理逻辑对应关系的问题,应该随便修改其中之一都能解决的!

你的问题跟线序没有关系,而是DDR[0:7] DQS0 DM0不在同一组。这个是没法解决的。改版吧。

你的意思是DQ[0:7]必须和DQS0 DM0在同一组,DQ[8:15]必须和DQS1 DM1在同一组,而我原来的接法是相反的,是这样吗?

如果这样的话,是不是DDR的数据总线顺序跟DDR芯片本身pin定义的顺序没有关系,完全由ARM来决定,是这样吗?

ST这种原厂都是这样,产品厂家要按照他推荐的做,不然产品出来会遇到各种问题,稳定性、死机或者各种莫名其妙的问题,他们都会往这上面扯,说没按照他们的来。

他们一方面是要是一个厂家一个做法,他们不方便维护,也不方便出底层软件。

请教你下,为什么字节内的顺序更改是不用改软件的呢?顺序乱了,不修改软件数据接收的时候不也乱了吗?请指点,谢谢。!

mark