请教个关于JTAG链路设计的问题

时间:10-02

整理:3721RD

点击:

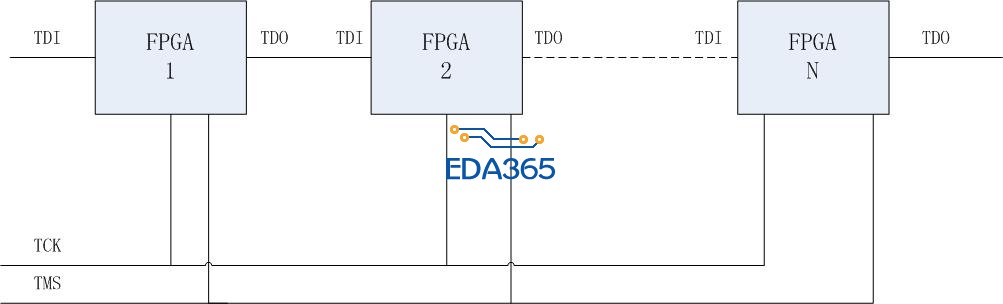

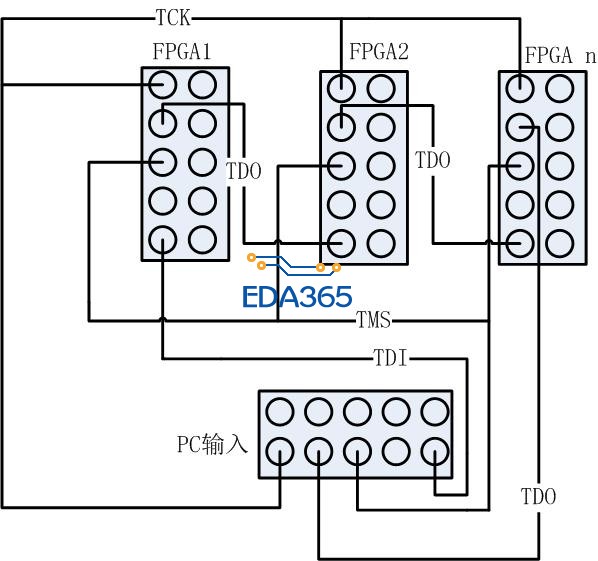

各位前辈好,最近小弟手头有个项目是设计一个JTAG链路的接口板,目的是对公司的一批同样的板子同时进行配置,我大概有了一个构思,原理示意图和连接示意图如下图所示。但是我之前没有过相关的设计经验,想请问大家这种接口板在设计的时候需要注意些什么,比如在什么信号前需要加buffer,tck用不用做等长等等,还是简单的连接就能实现功能呢?希望有相关设计经验的前辈不吝赐教。

原理示意图

连接示意图

木有人指导一下吗,顶一下

JTAG本身就支持这样级联....有这样级联过2片CPLD,没有发现问题。

恩,我这个可能得接8块左右,而且是不同的板子,怕加了buffer也会出问题

FPGA配置不是要用AS口么?

我们一般都是在板内做jtag链的。你的好像不是,所以要考虑 你最终的应用场景。

1、一定要共地,需要系统级考虑;

2、tck等使用20MHz以上频率,跨板传输信号质量风险有,buffer必不可少。

3、考虑最终场景,一定条件下tck、tdi等信号需要等长。例如,tck 20mhz,50ns周期,信号1米延时6ns,考虑下自己系统的信号延时有没有达到这个量级,尽量规避。

4、链路上预留调测电路,修正信号质量等。

多谢建议,的确不是板内的,是通过转接板实现多板间调试,所以比较复杂

我们这边一直都是JTAG调试,AS口没有用过……