边沿斜率dt/dv问题请教

时间:10-02

整理:3721RD

点击:

从信号完整性角度考虑,上升时间越短,高频分量越多,设计中尽可能选择边沿速率较低的器件。

从驱动能力角度考虑,信号变化沿越缓,处于非稳态时间越长,对器件工作稳定性越不利。

芯片数据手册中的边沿斜率在设计中有什么指导意义?是要求驱动端信号的边沿斜率大于这个值,还是要求驱动端信号的边沿斜率小于这个值?

从驱动能力角度考虑,信号变化沿越缓,处于非稳态时间越长,对器件工作稳定性越不利。

芯片数据手册中的边沿斜率在设计中有什么指导意义?是要求驱动端信号的边沿斜率大于这个值,还是要求驱动端信号的边沿斜率小于这个值?

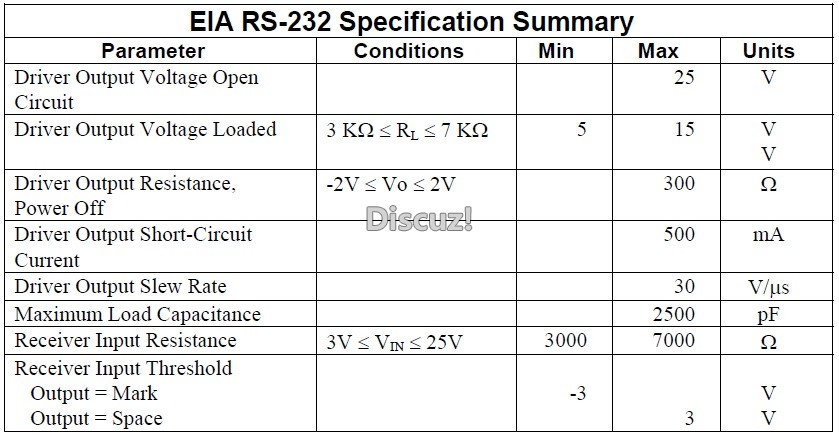

EIA RS-232 Specification Summary

偽雞百科(Wikipedia)

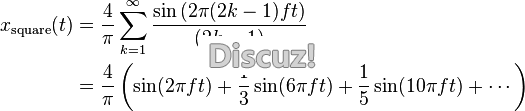

In electronics, slew rate is defined as the maximum rate of change of output voltage per unit of time and is expressed as volt per micro second.

从信号完整性角度考虑,确实是这样的。 我在资料上看到:

“输入信号必须满足输入信号边沿变化率的要求,只有信号满足此要求,逻辑器件才能可靠的识别出输入状态的变话,并做出有效地反应。信号变化沿越缓,则处于非稳态的时间越长,对器件工作的稳定性越不利”。

这段话是不是可以这样理解,对于给定的接收端,对驱动信号有最低边沿速率的要求?

狗版的square wave非常形象。