上拉 上拉电阻疑问

时间:10-02

整理:3721RD

点击:

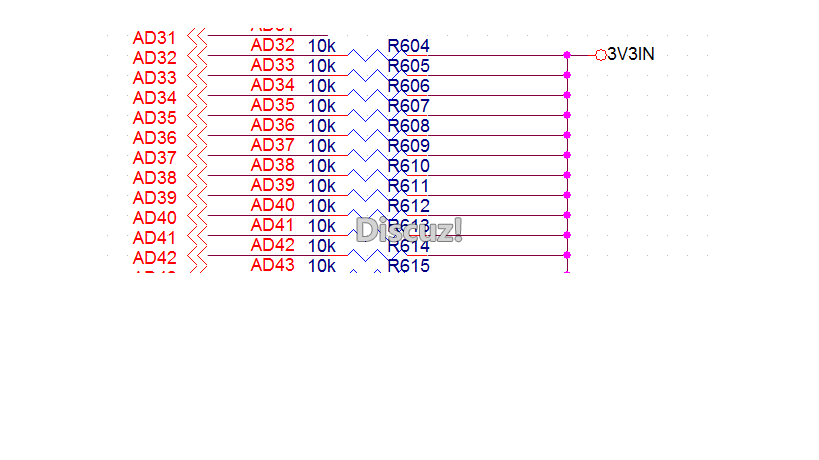

上拉就是将不确定的信号通过一个电阻嵌位在高电平----------图片中3V3IN上拉通过10K电阻连接到信号上,能否把电阻去掉?3.3V直接与信号相连?求大神解惑、、

上拉电阻是在你系统初始时怕你的信号不确定状态而导致一些不必要的问题才接的 就是初始信号默认为高 对你使用中的信号基本上无影响(上拉电阻太大或者太小会导致输出电流对信号产生影响)

你直接接电源就相当于把信号一直拉高 而导致你无法操作的

接个上拉电阻就是初始为高 使用中你设置高就是高 低就是低

哦 貌似有点理解 vcc通过电阻一直存在,那如何设置信号上的高低呢?通过信号线上电平变化?

信号直接接电源?你拿信号引脚当电源引脚使啊。上拉电阻是保证后级高电平使能(或有效)信号在上电(复位)之初就可以准确捕获电平的。确保信号输出后在整个传输路径中不受外界干扰而产生波动,简单来说就是把信号的高电平嵌位在3.3V,使信号幅值在0-3.3V之间变换。

这个上拉电阻的阻值如何进行选择呢?

看引脚能接受多大的电流