DDR参考电压被拉低,求大神解析

时间:10-02

整理:3721RD

点击:

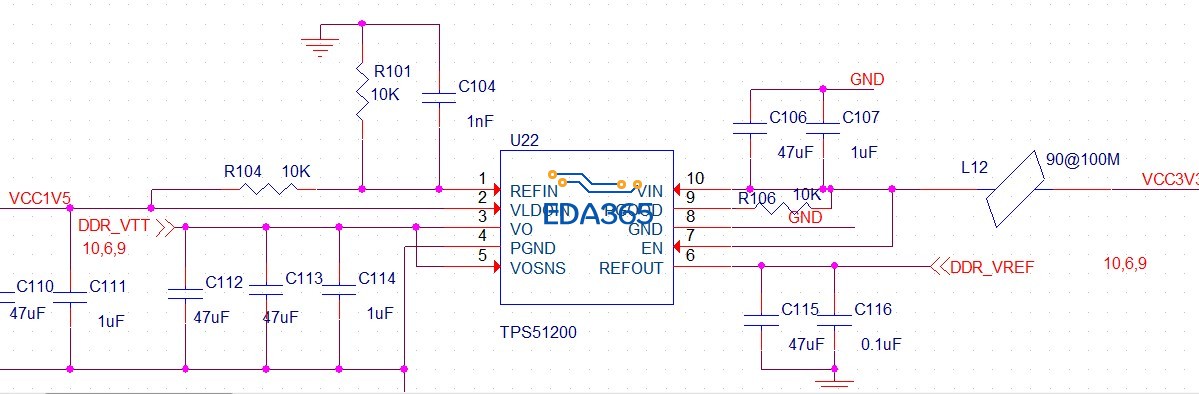

一个板子挂了四个ddr3,vref电压这个0.75v的电压在DDR跑起来之后变成只有0.2v,有些变成1.0v,代码在

另外一个项目的板子验证过是ok的,实在不理解为什么?

把vtt这个电压和vref这个电压飞线连接起来,ddr测试程序ok!,但是不明白vref怎么会被拉低?求大神指教。

另外一个项目的板子验证过是ok的,实在不理解为什么?

把vtt这个电压和vref这个电压飞线连接起来,ddr测试程序ok!,但是不明白vref怎么会被拉低?求大神指教。

Vref的电流很小,仔细量一下芯片管脚,看看有没有被烧坏的吧

没有,5块板子都是一样的情况,把VTT和vref飞线连接起来就什么问题都没有。

你用不是用分压的吗?VREF=2/1VDQS,好像是

是你的C115太大了,把它移走试一下吧。

电容不是越多越大越好,有时间看看datasheet。

去掉了,也不行。

你把CPU和DRAM那部分的图也上传过来吧。

R106改成100K试试,参考设计是100K的

学习了

lz请把图完整贴出,否则没法分析,只能猜。

小编的DDR_Vref 是U22输出的吗,U22是否是提供DDR_VTT和 DDR_Vref 的电源芯片?

我之前做的DDR_Vref 要么是用DDR_VTT分压产生,要么是从CPU自动输出,没有像小编这样做过。

另上DDR_Vref 电流很小,应该不存在电流不足被拉低的可能性。

L12作为一个磁珠在电源的输入端,是否怀疑过?

换了。不行。

CPU是用xilinx的spartan6 150t,目前不方便上传。

参考设计就是这么弄的。VTT及VREF都是这个芯片产生的,另外一个项目也是这么接,唯一的不同是这个

板子挂了四个DDR,另外一个是三个DDR。

CPU能输出VREF?