求狗粮!输入、输出电容是用来表征什么的参数?大家说说自己看法

CI,对于一个输入管脚,就相当于这管脚并了一个CI大小的电容?信号由低电平到高电平就是相当于把这电容充电?从低电平充到VIH的时间跟驱动电流有关?信号频率一定的情况下,CI越大是不是需要的驱动电流越大?芯片管脚的信号频率越高CI是不是就越小?CO又怎么理解?

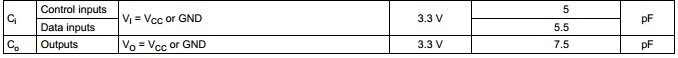

CI CO

自己顶

CMOS Logic Dynamic Power

The device dynamic power requirements can be calculated by the equation:

PD = (CL + CPD) x VCC2 x f

where:

PD = Power dissipated in mW

CL = Total load capacitance present at the output in pF

CPD = A measure of internal capacitances, called power dissipation capacitance, given in pF

VCC = Supply voltage in volts

f = Frequency in MHz

- CIN : Input Capacitance - The parasitic capacitance associated with a given input pin.

- COUT : Output Capacitance - The capacitance associated with a three–state output in the high impedance state.

- CL : Load Capacitance - The capacitor value which loads each output during testing and/or evaluation. This capacitance is assumed to be attached to each output in a system. This includes all wiring and stray capacitance.

一句話............不會!

UP UP

顶一下,别沉了!

好啦!來結案一下,我讀了幾篇文章心得如下,若有錯誤請大家指正。

CIN 和 COUT 是半導體製造時伴隨出現的寄生電容(Parasitic Capacitor)。

就樓主的認知來說,CIN 或 COUT 越大驅動電流會越大,這是對的,如我在三樓所貼的公式。唯一需要修正的是,影響驅動電流(Driving Current)的是負載電容 CLoad,它代表 CIN + COUT + CStray(PCB 雜散電容)電路中各種電容的總和,而不是單獨 CIN 或 COUT 的影響。

CIN 和 COUT 的值雖然會會跟著訊號頻率變化,但並非差異很大。所以第二句話個人覺得應該反過來講,如果你需要比較高的工作頻率,IC 需要比較小的 CIN 和 COUT 值。同樣這個影響也是看 CLoad,非 CIN 或 COUT 單獨的影響。

电容越大,越差!

影响速度!

这不是L波!电容越大,带的负载越重

超級狗回答的很棒,但我補充一下:

1. CI,对于一个输入管脚,就相当于这管脚并了一个CI大小的电容?

=: ) 也不好說是管脚并了一个CI大小的电,應該說是输入管脚電路天生及寄生的電容值和。

2. 信号由低电平到高电平就是相当于把这电容充电?

= 是

3. 从低电平充到VIH的时间跟驱动电流有关?

=: ) 是,電容的電壓與充電電流成正比。

4. 信号频率一定的情况下,CI越大是不是需要的驱动电流越大?

= 信号频率一定的情况,你這個頻率不知怎麼理解,對數字電路而言,信號的上升一個 duty 時間內應該要充電到超過 VIH,若不能就會錯失這個 bit,只要 Ci 越大前級的驅動電流就要越大。

5. 芯片管脚的信号频率越高CI是不是就越小?

= 是的,芯片管脚可接受的信號頻率越高, Ci 越小。

6. CO又怎么理解?

=:) 就是芯片输出管脚電路天生及寄生的電容值和。

“信号频率一定的情况下,CI越大是不是需要的驱动电流越大?”

信号有一个setup时间的要求,通常频率越高这个时间就越小,我说的信号频率一定就是指这个setup时间一定。

Setup 的時間要求與所用的邏輯電路有一些關係,當然運作更高速的芯片,就會用更高速的電路架構或小一些的物理尺寸的電晶體 (三級管),以縮短 Flip-Flop 的 Setup/ Hold time,而 Setup / hold time 的時間要求,通常是取決於 Logic gate 的傳輸延遲,而 Ci的大小通常是受 input buffer 影響, Ci 大小影響信號的斜率,所以也會影響到時序,但就內部電路而言,它並不會改變 Flip-Flop的 Setup / hold time 的大小要求。