差分对的两条线能画在两个不同层不?

这么走不蛋疼吗,临层可以,隔了两层不行。

差分对要求走在同一层;并且要考虑等长、Z抗。三个基本一定要做。

有的差分线由于IC及布局的原因实在是没办法走在同一层,我的6层板就走在top和第3层。好像是不能走相邻层吧。

如果速率不高,看按一般阻抗线走行不行?可以试试!

有这样设计的,但是要求在同层回流,很难做到,否则违反差分原理。

差分是为了啥?这样设计还要差分干嘛

没听说过这样的设计。

走层间差分也是可以的.

不过在TOP/BOTTOM 是不可能的.

个人觉得,如果速度不是过高,你可以分开走,都参考同一参考平面。等长控制好就OK。因为我曾经看过一篇文章,说差分对的间距可以很大……一般更多的是要求等长,连续参考平面

低速无所谓,你想怎么走都行,高速就有要求了,等长还是等距。

绝对不可以隔层的。

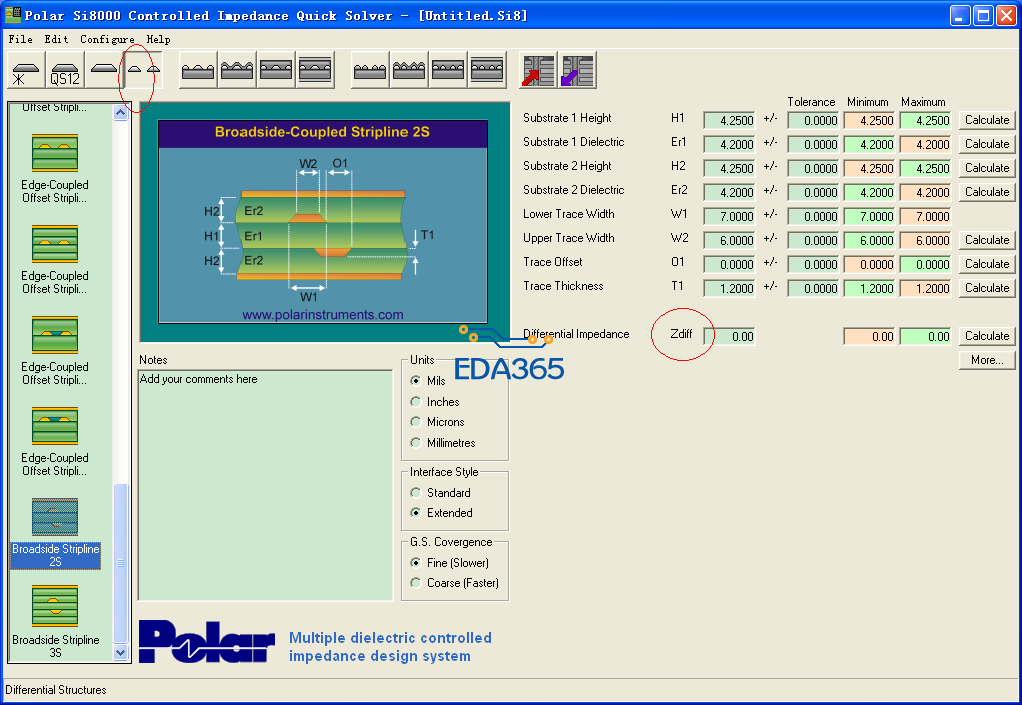

但是能不能临层,我也很纠结,绝大多数人说差分必须走在同一层,但是请看下图。

我不知道这是不是差分线模型!

临层差分

这当然也是一种可作为differential trace的布线方式,不过相比较于edge coupled,broadside coupled在very high speed以及pcb 制作上,以及抑制noise都不好。

1、正常broadside coupled striplines需要route在vdd and vss之间,signal trace必须经过vdd,这样很容易拾取vdd plane的noise

2、若上下都是vss,这就要增加layers以及cost

3、pcb板厂精确对齐adjacent signal layers也是有工艺要求的,否则小的偏差会改变differential impedance。

4、非紧耦合的differential trace在受到common noise干扰时,受影响的程度会不一样,差分性能就下降了阿。

所以不得已是不会在adjacent(相邻层)或者separate(隔层) layers上走差分线的,ls有位说得对阿,低速且不是low voltage时可以勉强用。

一家之言,欢迎拍砖。

邻层走差分也是可以的。从立体角度来看的话,邻层走差分也是没有问题的,只不过中间隔了一层介质,其他因素都没有变化。如果一定要走在邻层的话,需要考虑这对差分线的参考平面,严格对称性。对工艺要求比较高。

1、如果叠层是对称的,并且信号参考层都为GND的话,这样两根线的回流路径及参数基本都是一样的,但如果制板工艺控制不严格,很可能会影响差分线的性能。

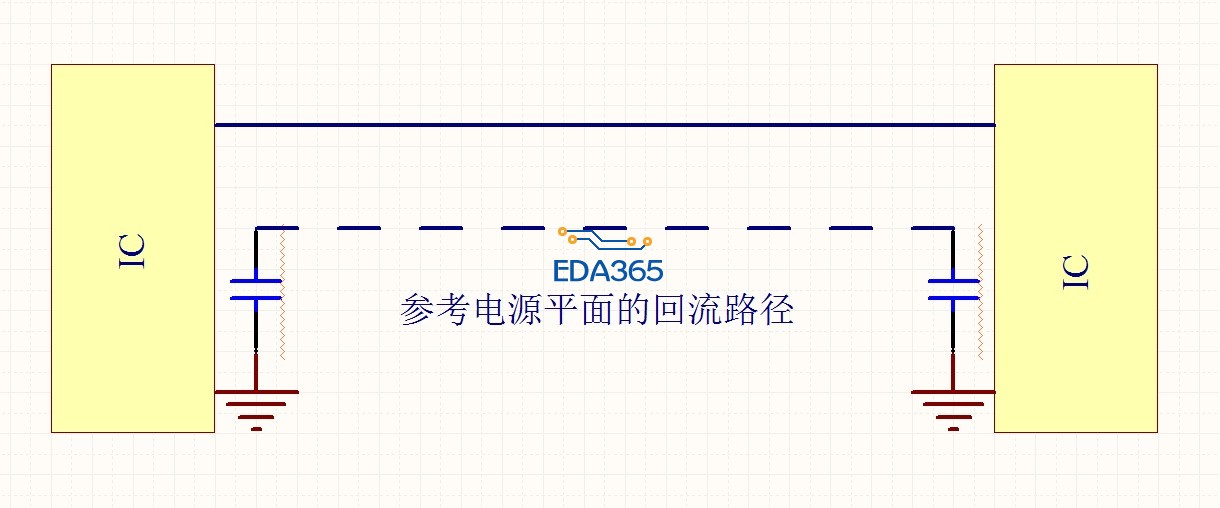

2、如果叠层是对称的,并且信号参考层都为PWR的话,这样两根线的回流路径及参数不一定是一样的,要看具体去耦电容的位置才能决定其回流路径,同样也会想楼上说的一些干扰因素在里面。

3、如果是对称参考层不同的话,一个信号参考层为GND,另一个信号参考层为PWR的话,这样的两根线的回流路径是不一样的,是会有影响的。参考GND的信号回流自然很容易回流,但是参考PWR层的信号就不一定了,需要根据去耦电容放置的位置来确定它的回流路径,这种做法的影响是比较大的。不建议采取。

听过,可是还没坚果 这么走得