一个关于串接电阻的作用问题,求大神指教

时间:10-02

整理:3721RD

点击:

我看到周立功的以太网接口电路的时候,由于FPGA的数据、地址线要和以太网芯片RTL8019AS相连,但是以太网芯片的供电电压为5V,而FPGA的IO口却只有3.3V,文献上就说因为这个原因,于是在数据、地址以及控制线都串接一个220ohm的电阻,这个电阻的作用是什么啊?望大神给个详细讲解!多谢

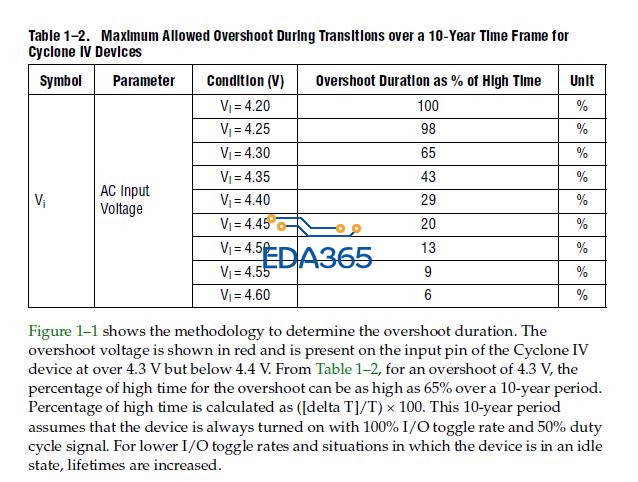

看上面这个题你就知道,输入电压高了对器件寿命是有影响的。

This 10-year period

assumes that the device is always turned on with 100% I/O toggle rate and 50% duty

cycle signal. For lower I/O toggle rates and situations in which the device is in an idle

state, lifetimes are increased.

再来看看上面这个图 FPGA 开启内部弱上拉电阻的阻值。

可以看到3.3V下, 最小7K 典型25K 最大41K ,

如果和FPGA连的那个芯片可以设置为开漏输出,或内部弱上拉或外接上拉电阻10K,47K,

FPGA和芯片之间串联一个数百-数K的电阻

按这个算到FPGA PIN上的电压按分压算,算出来看看是多少? 在PIN 定位到有PCI钳位二极管的bank中,这样就万无一失了。

限流。这个说法我觉得比较靠谱的。有时候对于3.3V和5V电平信号连接的时候,有人就不用电平转换电流,直接串联一个电阻来限流!

恩,是的哦,懂啦,谢谢啊,应该就是对5v电压起一个降压的作用!

不想用芯片,又不想换3.3V的芯片,串联电阻就是这个办法。

严格说这种接不好,哈。

有些FPGA他有个内部二极管钳位的,PCI钳位 可以把它开起来,在接下限流电阻,5V输入,到FPGA就4.3V了。

这个对于我有点高深,谢谢你的指教,我再去研究研究,我还不知道有个二极管钳位

看上面这个题你就知道,输入电压高了对器件寿命是有影响的。

This 10-year period

assumes that the device is always turned on with 100% I/O toggle rate and 50% duty

cycle signal. For lower I/O toggle rates and situations in which the device is in an idle

state, lifetimes are increased.

搜噶,懂啦,谢谢啦!学习了

再来看看上面这个图 FPGA 开启内部弱上拉电阻的阻值。

可以看到3.3V下, 最小7K 典型25K 最大41K ,

如果和FPGA连的那个芯片可以设置为开漏输出,或内部弱上拉或外接上拉电阻10K,47K,

FPGA和芯片之间串联一个数百-数K的电阻

按这个算到FPGA PIN上的电压按分压算,算出来看看是多少? 在PIN 定位到有PCI钳位二极管的bank中,这样就万无一失了。

不知道,这么理解可以?PCB设计中的阻抗匹配问题。

CPU和FPGA链接时,比喻地址线,数据线,控制线,信号在传输过程中,都会有干扰。

如果一个信号的边沿非常陡峭,容易产生过冲。串联电阻与信号线的分布电容以及负载输入电容等形成一个RC电路,这样就会降低信号边沿的陡峭程度。