亟待高手解答

誰說的?

高頻的東西,把地掏空、只留電源層試試看!

不太明白狗老大的意思?能说的具体点么?

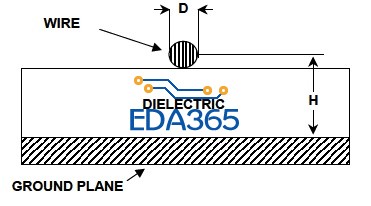

樓主講的應該是有些 Stripline 或 Micro Stripline 文章中的這段話︰

Note that the figures below use the term "ground plane". It should be understood that this plane is in fact a large area, low impedance reference plane. In practice it may actually be either a ground plane or a power plane, both of which are assumed to be at zero ac potential.

但注意到最後一句,電源層交流電位(Power Plance AC Potential)要為零才能符合條件。現實世界中沒有電源層交流電位(Power Plance AC Potential)為零的環境。電路中有處理器(CPU)、內存(Memory)、邏輯閘(Logic Gate)......工作時會產生電流擾動。除非負載是一個純電阻,這樣交流電位(AC Potential)就會是零。

所以,以敝公司射頻(RF)人員的設計習慣,一定都是參考地、而不是電源層。四層板阻抗線走背面,第三層(VCC)掏空、參考第二層(GND)。

谢谢狗老大,不过还是不太明白什么叫電源層交流電位(Power Plance AC Potential)?

就是你電源層不能有交流電流,有電流變化微觀上電位也會跟著變化。

我們觀念上電源層等電位,是假設銅片很大、電阻為零,但微觀上銅片上還是有電阻,電流流過就會有電位差。

原来如此,多谢了!

看什么类型的电源和什么类型的信号了。内层的信号,一般两个参考平面,一边是地,一边是电源,也没事的。参考平面是做个回流和阻抗控制的。如果是四层板,不是射频信号,电源波动也不大,完全可以参考电源层。如果信号要求高,一般没人选择四层板设计的。

FM 75MHz 開始就有了,AM 更低到 500KHz!

^_^

Power Plance AC Potential要为零是不是可以这样理解,比如电源层是3.3V的,整个板子上会有很多3.3V的滤波电容(0.1uf,0.01uf),这样是不是可以近似的理解为Power Plance AC Potential为零? 所以如果非要参考电源层的时候必须在该走线附近加些电容。 不知道这样理解对不对?

他问题里面没说啊

参考哪一个平面是可以选择和优化的,以DDR3-1066 UDIMM Systems设计为例,若芯片内部某IO Pad参考的是电源平面,则应确保trace以power为参考面,已确保最小回流路径。

Board Stack-Up

Freescale recommends placing all DDR signals on critical layers that are ground-referenced, which ensures the lowest impedance for the return currents and provides improved signal integrity performance.

我想大家繼續搞下去,可能連鐵框(Metal Can)也能 Reference。

向射頻(RF)主管請教了這個問題,他說理論上是對。但要放多少濾波電容才能達到顯著的效果,值得商榷!

理论上只要是个平面就可以参考,哪怕是没有网络的铜皮。但是回流路径到芯片引脚附近时候,最终要回到芯片的地上,需要让这个参考平面和芯片的地形成低阻抗的交流通路,也就是加无穷大的电容。不然就会出现阻抗不连续。 所以最理想的,就是直接参考一个完整的地。 参考电源的话,最终的回流照样是通过去耦电容回到地的。