IIC电平为什么会被拉低?

应该是上拉电阻的阻值大了,换个小的试试……

上拉电阻本来是10K的,我换了个4.7K的上拉,依然不行

IIC的电平被拉低至多少?

上拉电阻接1K,电压被拉低至1.16V。

除非有芯片被击穿,否则不会被拉低。你说的是I2C在通讯的时候,直流电压测量是1.16V吧,说明有信号和时钟在走,这是对的,用示波器一看就知道什么回事了。

查一下另两组接口的资料。仔细看看。曾碰到过类似的问题。最后是更新了另外一组的代码就搞掂了。那一组的IIC在不上电或没复位的状态下是低的。

我也这么认为,所以有跟软件工程师沟通过,但他们说另两组在不通讯的时候,是设置为1的。用示波器测试过波形,CLK,DATA波形都是正常的,就是电平有3.3V变为1.14V。

明显的被软件当作IO在操作

另外两组IIC 的IC 有没有供电?如果没有供电,会将电压下拉。

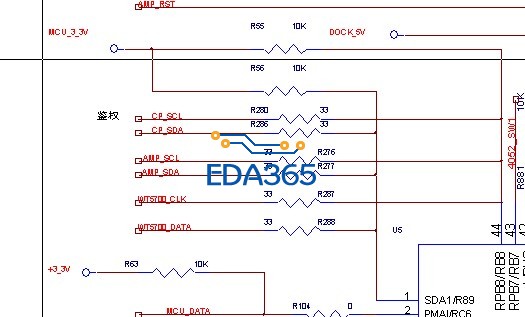

可能发原理图上来,大家参考一下,也可以拆掉不同的组,很容易搞掂

去掉另外两组IIC,依然无法正常通讯,所以我在想,是不是需要三组IIC同时通讯,才可以正常运行?!按理说,各组IIC是互不影响的。在standby下,只有触摸IIC WT5700正常供电。

I2C 的雙向架構是由兩個部份所構成,送的部份是一個 Open Collector 或 Open Drain 線路;收的部份則是一個 CMOS Input線路和前述的 Open Collector 或 Open Drain 線路並接在一起。

當你不給電時,Open Collector 或 Open Drain 的電晶體(Transistor)Gate 沒有電壓,電晶體有可能處於半開或全開的狀態。

另一方面 CMOS 線路沒電時,電晶體(Transistor)Gate 沒有電壓,電晶體也是可能處於半開或全開的狀態。

如果你的問題是其它 2 個 I2C Device 給電就不會發生,那就應該是漏電把電位(Voltage Level)拉低的。

任何 IC 如果沒特別說明不給電時 I/O 腳位是高阻抗(Hi-Z 或 High Impedance)狀態,都有可能會透過 I/O 接腳造成漏電。

如果你的設計為了省電,會有部份系統斷電(Partial System Power Off)的需求,一般我們的解法是去找一顆有電源隔離(Power Isolation)Buffer 或 Level Translator 把 Bus 兩端的 Device 隔開。

所謂有電源隔離(Power Isolation)的 IC,是這種 IC 會個別吃兩端系統的電源,當任一邊的電源消失時,IC 所有的I/O 接腳都會變成高阻抗(Hi-Z 或 High Impedance)狀態,這樣就可以防止漏電的情況發生。

詳細您可參照TI I2C Level Translator TXS0102 的 Datasheet!

http://www.ti.com/lit/ds/symlink/txs0102.pdf

如果你所謂的去掉 2 組不供電的 I2C 是把 33R 電阻拿掉,但其它 2 個不給電的 Device 還是有其它接腳和 MCU 或其它有電的 IC 相連,這樣還是有可能有漏電的危險。

漏電造成 IC 不完全或是不正常的工作!

其實你只要用電錶量其它 2 顆不供電的 IC 上的電源或 I/O 接腳,只要能量到一些類似 0.3V、0.6V 這種微弱的電壓,那就表示有漏電的狀況發生了!

漏得嚴重的還可能會量到超過 1V。

按小编的意思是取掉其它两组的电阻,在STANDBY状态下,IIC电压还是低的。那就去查程序吧。