关于DDR3 时钟线上的电阻电容的作用

时间:10-02

整理:3721RD

点击:

各位大侠:

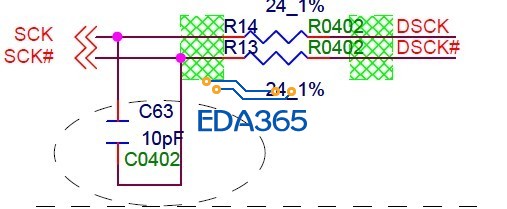

请教一个问题,关于DDR3 时钟线上的匹配电容,这个电容的作用。我现在做的是4片DDR3,一般情况下去掉C63这个电容或者上这个10pF的电容,DDR都能跑起来,速度的话跑480M也没有问题,但有时候,某些PCBA上就需要匹配这个电容,加上这个电容可能效果不怎么好,去掉效果更加。有时候某些板却要匹配更小的电容,才能下载。关于这个问题,一直很困扰我。有两点很困惑:

1、这个电容的作用,电容的大小对DDR的影响?

2、为什么某些PCBA需要去做这样的匹配,DDR才能跑起来,并且电容的值还不一定相同?

对这部分电路确实还是很迷惑......

请教一个问题,关于DDR3 时钟线上的匹配电容,这个电容的作用。我现在做的是4片DDR3,一般情况下去掉C63这个电容或者上这个10pF的电容,DDR都能跑起来,速度的话跑480M也没有问题,但有时候,某些PCBA上就需要匹配这个电容,加上这个电容可能效果不怎么好,去掉效果更加。有时候某些板却要匹配更小的电容,才能下载。关于这个问题,一直很困扰我。有两点很困惑:

1、这个电容的作用,电容的大小对DDR的影响?

2、为什么某些PCBA需要去做这样的匹配,DDR才能跑起来,并且电容的值还不一定相同?

对这部分电路确实还是很迷惑......

我的理解是消除差模干扰

1. 这个电容主要是消除DDR CLOCK的OVERSHOOT AREA, 以满足JEDEC的要求;

2. 我觉得去掉这个电容,DDR都能跑起来,只是overshoot多了一些,内存芯片热一些的区别,这个电容应该放在内存的接收端,而且,如果480Mhz的DDR3,以我的经验来看10p还是大了一些,应该3-5pf会好一点,大了就有点过了。电容当然和频率有关系,不同频率用的值应该不一样,具体值要看测试结果。

个人认为此电容与前面电阻一起构成L型滤波电路,可以滤除一些高干扰和高频过冲等,使信号时钟信号波形更好!

哦,那电容的大小取值方面有什么讲究么?

应该就是几PF就可以了。

文章不错,学习了!

了解一下,深度不懂

学习了

多谢分享!

各位我认为电容它就是个随着频率改变的阻抗,给不同频率成分做了不同差分匹配呀,频率越大,意味着容抗越小呀,想想大家应该能明白是咋回事,不想电阻跨接,它是全频段的。

我们一般在CLK上是串R,在两个差分线上预留一个位置,不过不是放C,而是放R,做到阻抗匹配。特别是两层板的时候。

电容应该是消除差模噪声,而电阻如果是串联的话应该是满足阻抗匹配。如果是上拉,那就是ODT,(这个是用于memory down的情况);