在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。

时间:10-02

整理:3721RD

点击:

在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。

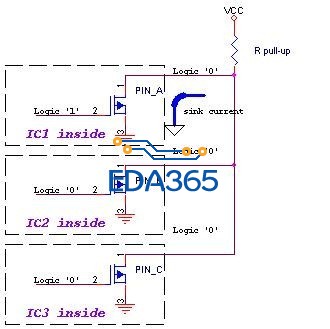

所谓“开漏电路”概念中提到的“漏”就是指MOS FET的漏极。同理,开集电路中的“集”就是指三极管的集电极。开漏电路就是指以MOS FET的漏极为输出的电路。一般的用法是会在漏极外部的电路添加上拉电阻。完整的开漏电路应该由开漏器件和开漏上拉电阻组成。如图1所示:

组成开漏形式的电路有以下几个特点:

1. 利用外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。IC内部仅需很小的栅极驱动电流。如图1。

2. 可以将多个开漏输出的Pin,连接到一条线上。形成“与逻辑”关系。如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。这也是I2C,SMBus等总线判断总线占用状态的原理。

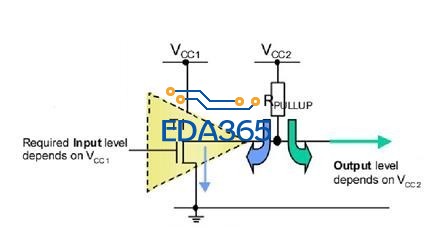

3. 可以利用改变上拉电源的电压,改变传输电平。如图2, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了。

4. 开漏Pin不连接外部的上拉电阻,则只能输出低电平。

5. 标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。

应用中需注意:

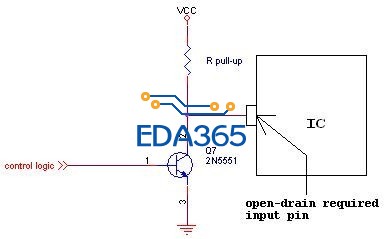

1. 开漏和开集的原理类似,在许多应用中我们利用开集电路代替开漏电路。例如,某输入Pin要求由开漏电路驱动。则我们常见的驱动方式是利用一个三极管组成开集电路来驱动它,即方便又节省成本。如图3。

2. 上拉电阻R pull-up的阻值决定了逻辑电平转换的沿的速度。阻值越大,速度越低功耗越小。反之亦然。

不错不错

归根到底还是器件的原因,场效应管和三极管的区别,前者是电压决定电流的器件,后者是电流决定电流的器件;前者是栅极,源极,漏极,后者是基极,集电极,发射极。

受教了

有人做个总结还是不错,呵呵

说的不错