讨论下关于SDRAM的等长布线要求

以上图管脚为例子,每组信号的要求,图片是网上截取DDR的。

讨论的焦点:是否需要严格的等长,或者某个误差范围内的等长,或者不必须等长

上传一份网上的资料

1.建立时间和保持时间,这里说的建立时间和保持时间是针对接收端而言的,建立时间(SetupTime)指的是数据在时钟沿到达之前必须保持稳定的最小时间,保持时间指的是数据在时钟沿到达之后必须保持稳定的最小时间,建立时间和保持时间对接收端的IC来说是个必须要满足的参数,否则采集就会出错或不成功,因为IC内部采集和处理数据的逻辑门和连线需要时间,否则触发器在数据还没有稳定的时候会有误触发。

2.发送端和接收端的时序,对于发送端来说,每个时钟周期都要发送数据,并且是时钟沿到来就启动发送,但对接收端来说,任何时钟沿采样的数据,都是发送端前一个时钟发送的数据,理解这一点是非常重要的。

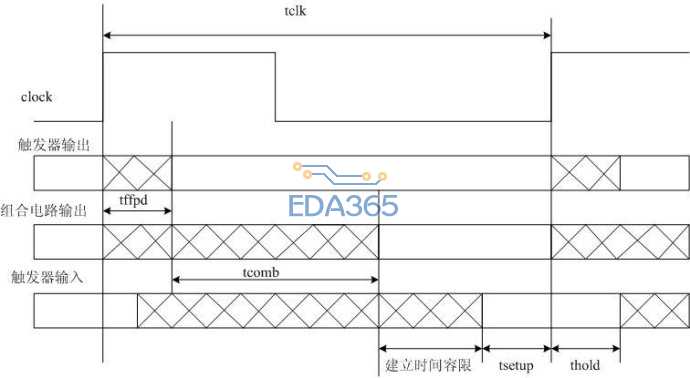

3.建立时间容限和保持时间容限,了解layout导线延时就必须理解建立时间容限和保持时间容限,因为满足建立时间容限和保持时间容限的的导线延时都是可以接受的,不会影响电路逻辑关系的,理解这些关系,参考下图理解:

上图为网上截取。

建立时间容限如图,保持时间容限为tffpd + tcomb - thold,上图上中间的表示的是输出端的时序,最后一个表示的是接收端的时序。

layout导线延时的容许范围就是:|data - clock| <= 建立时间容限与保持时间容限的最小值

具体以SDRAM为例子加以说明:

1.SDRAM的时序如下图

首先看,DATA(OUT) 图中tTENDAT = 0,即对发送端而言,时钟沿到达立即发送数据,tDSDAT = 4ns,说明数据正在发送时在时钟沿到后的4ns时发送的,即保持时间容限 = 4ns - 0.8ns(保持时间tSDAT),建立时间容限 = 7.5ns(tSCLK时钟周期) - 4ns(总线上有新的发送数据的真正时刻) - 1.5ns(tSSDAT建立时间) = 2ns

以6inch/ns的传播速度计算,数据线和时钟线的导线长度可以相差2*6=12inch,这是个非常大的容差范围,所以SDRAM根本无需做等长处理。

这个是他理解。我现在也处理这方面的走线,以前的ARM版走线的时候,虽然误差有点大,但是没出过问题。

我按照DDR的要求来布SDRAM的线有点纠结。

大家讨论讨论吧!

上面资料转载于一位叶冲茂的博主。注明过了,希望不要介意

FR-4板材的介电常数4.7,133MHz信号在FR-4上的波长大约是1米,只要引线长度相差不超过1/10波长(10cm),就不会对信号完整性有什么影响。

网上看到的。

论坛里面也说不超过4000mil理核心芯片近点也不必须等长。现在还没个底。芯片资料里面也没说,时序图看了也就这样了

“以6inch/ns的传播速度计算,数据线和时钟线的导线长度可以相差2*6=12inch,这是个非常大的容差范围,所以SDRAM根本无需做等长处理。”

我布线时,手机板的RAM也是用SDRAM的,地址和数据线布线时只要求在L2中布完就可以了,所以在找SDRAM 布线规则。

信号在介质中的传播速度是多少?6INCH/ns是怎么得来的?

按说信号属于电信号,光和电信号应该属于同一个性质吧,那光在空气中的传播速度是3*10^8,那在4.7的介电常数的介质里呢?

我之前做SDRAM,165MHz,基本不考虑长度影响,连上就好了。主要是考虑电磁屏蔽和电源。

這些說法不會太武斷了嗎?

這些時序上的問題基本是是要看晶片本身的訊號來決定 , 如果晶片本身的Tr , Tf 很小的話 , 那我想不出問題都很難.

如果 Tr, Tf 時間充裕的話, 那要出問題也不容易.

當您的佈線長度與訊號的 SR 值之間尚無法構成傳輸線問題時 , 根本沒問題.大家的訊號可視為同步.

但這個條件一直壓縮下來時 , 問題就出來了. 所以一般真的會要求時序等長的控制大多在較高速的訊號上.

xue xi le

谢谢

你的波长算错了吧,波长等于c除以f,所以应该是2.56m,十分之一波长是0.256m吧,

哦,我错了,忘记除根号4.7了,呵呵。

想请教兄台,如果是flash呢?它的数据位,地址位布线时要不要考虑等长问题呢?

SDRAM 不需要严格意义上的等长。

FLASH 存取速度慢,更不需要等长

楼上说的有道理!

前辈,请教一下,屏蔽是否指是对数据线进行屏蔽?电源处理有什么药注意的?谢谢

一般来说,是对SDRAM部分的信号线进行屏蔽,空间小的时候,可以分组包地;如果条件允许,可以考虑全部包地。clk一定要包地,或是有好的参考平面,根据波形或者EMC要求,可以考虑串电阻或者并电容。电源主要是控制下纹波和噪声。SDRAM速率比较低,冗余度范围大,一般使用上问题不大。